D/A prevodník. .

Tieto zariadenia sú medzi sebou „vodiče“. analógový a digitálny svety elektriny.

Pointa je, že senzory, motory, svetlá a mnohé ďalšie zariadenia používajú analógový signál, to je napríklad napätie s úrovňou od 0V do 12V zatiaľ čo digitálne FPGA, mikrokontroléry a mikroobvody potrebujú konštantné úrovne napätia, napríklad 0V a 5V, ktoré sú logická 0 a 1 resp.

Príklad 1 DAC

Predstavte si, že stojíme pred úlohou ovládať jas LED:

- 10 úrovní (gradácie) jas LED

- maximálne napätie cez LED 9V

- ovládané mikrokontrolérom a dvomi tlačidlami "+1 úroveň jasu", "-1 úroveň jasu"

LED dióda teda pracuje pri napätí 0 až 9V. Je ľahké uhádnuť, že 10 stupňov jasu je 10 úrovní napätia, ktoré aplikujeme na LED - 0V, 1V, ..., 9V

Výstup mikrokontroléra je buď 0V alebo 5V. Ale nie 1V, 3V, 4V alebo 9V. Ale mikrokontrolér má veľa logické závery, s ktorými sa môžeme spojiť DAC v a konvertovať logika v analógový signál.

o digitálno-analógový prevodník sú tu napríklad 4 vstupné piny pre pripojenie logických signálov a 2 piny pre výstup analógový napätia od 0 do 15V - závery "+" a "-".

Tu je vaša práca DAC a: keď podávame všetky 4 nohy logický 1, potom úroveň napätia analógový výstupný signál je maximálny ( 15V v našom prípade), keď podávame 0 - minimum, t.j. 0V

Teraz to najzaujímavejšie. Každá vstupná svorka DAC ale existuje "váha" pre výstupný signál. Napríklad vrchný výstup „váži“ 8V (to znamená, že ak použijete logickú 1 len na 1. výstup, tak na výstupe dostaneme 8V), ďalšie pod 4V, ďalšie 2V a posledné nízke 1V. Teraz spočítajte tieto čísla a získajte 15V.

Potrebujeme získať úrovne 0V, 1V, 2V, 3V, 4V, 5V, 6V, 7V, 8V a 9V.

To znamená, že vstupy DAC musia byť kódované podľa nasledujúcej tabuľky

| Napätie zapnuté analógový výstup | 0V | 1B | 2B | 3B | 4B | 5V | 6V | 7B | 8V | 9B |

| Vstup 1, hmotnosť 8V | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| Vstup 1, hmotnosť 4V | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| Vstup 1, hmotnosť 2V | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| Vstup 1, hmotnosť 1V | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

Tlačidlá "+1 úroveň jasu", "-1 úroveň jasu" pripočítajú alebo odpočítajú 1 jednotku od výstupu digitálny signál mikrokontroléra. Tento signál bude privedený na vstupy DAC. Výkon DAC bude pripojený k LED. Misia splnená!

Príklad 2. ADC

Analógovo-digitálny prevodníkfunguje opačne. Na vstup aplikujeme meniacu sa úroveň napätia, na výstupe dostaneme logiku (bitov) +5V a 0V, alebo logická 1 a 0

Nastavme úlohu na snímanie údajov zo snímača teploty:

- snímač ukazuje teplotu od 0C do 30C

- pri 0C má snímač výstup 0V, pri 30C má výstup 15V

- signál musí prijímať mikrokontrolér v digitálnej forme (logická 1 a 0, napätie + 5V a 0V)

ADC má dva vstupné piny pre príjem analógového signálu s napätím napríklad od 0 do 15V a v našom prípade 4 piny pre výstup digitálny logický signál. Teda štvorbitový paralelný kódový signál.

Výstup z nášho senzora pripojíme k analógovému vstupu ADC a digitálny štvormiestny výstup z ADC pripojte k mikrokontroléru. A na mikriku už prijímame odčítania zo snímača v digitálnej podobe. Údaje v procese budú zodpovedať tabuľke nižšie.

Analógovo-digitálny prevodník je zariadenie určené na prevod fyzikálnej veličiny, ktorá sa v priebehu času neustále mení, na ekvivalentné hodnoty digitálneho kódu. Analógovou hodnotou môže byť napätie, prúd, uhlový posun, tlak plynu atď.

Proces analógovo-digitálnej konverzie zahŕňa postupné vykonávanie nasledujúcich operácií (obr. 13.5):

Vzorkovanie hodnôt pôvodnej analógovej hodnoty v určitých daných časových bodoch, t.j. vzorkovanie signálu v čase,

kvantifikácia (zaokrúhlenie prevedenej hodnoty na niektoré známe hodnoty) hodnoty analógovej hodnoty získanej v diskrétnych časoch podľa úrovne,

Kódovanie - nahradenie nájdených kvantových hodnôt niektorými číselnými kódmi.

Ryža. 13.5. Princíp analógovo-digitálnej konverzie.

Chyba integračného ADC je určená najmä zmenou strmosti pílového napätia, ktorá je určená časovou konštantou RC integrátora (generátora pílového napätia). Vplyvom vonkajších destabilizujúcich faktorov, najmä teploty, sa časová konštanta a tým aj strmosť pílového napätia mení, čo vedie k výrazným chybám pri prevode. Preto sa v súčasnosti na budovanie integrujúcich ADC využíva princíp dvojitej integrácie.

Princíp činnosti dvojitá integrácia ADC spočíva v tom, že najskôr sa počas určitého pevného časového intervalu T1 integruje analógovo prevedená hodnota Ux a potom sa integruje referenčné (referenčné) napätie opačnej polarity Uop. Časový interval T 2 je úmerný prepočítanej hodnote U x.

Obrázok 13.11. Štrukturálny diagram ADC dvojitej integrácie (a) a časový diagram jeho činnosti (b) V priebehu časového intervalu T 1 sa totiž napätie na výstupe integrátora mení podľa lineárneho zákona:

Počas časového intervalu T 2 sa výstupné napätie na výstupe integrátora mení z Uout.int.max na 0, t.j.

teda

Časový interval T 2 teda závisí od konštanty T 1 /U op a premennej U x a nezávisí od parametrov integrátora. To je možné vidieť na grafe na Obr. 13.12.

Obrázok 13.12. Napätie na výstupe integrátora pri časovej konštante τ 1 = R 1 * C 1 (1) a pri τ 2 = R 2 * C 2 (1) ADC s dvojitou integráciou poskytuje vysokú presnosť prevodu v podmienkach priemyselného šumu v široký teplotný rozsah a je široko používaný v meracej technike a automatizovaných riadiacich systémoch.

Napríklad základom všetkých multimetrov je dvojintegračný ADC, vyrobený na čipe K572PV2 alebo K572PV5. Integrované obvody sú takmer rovnaké, ale prvý poháňa LED diódy a druhý poháňa LCD.

Mikroobvod K572PV2 spolu so zdrojom referenčného napätia, niekoľkými odpormi a kondenzátormi plní funkcie ADC s dvojitou integráciou s automatickým nulovaním operačného zosilňovača a určením polarity vstupného signálu.

Hlavné technické parametre IS:

Bitová hĺbka - 3,5 desatinných miest,

Vstupná impedancia - 50Mohm,

Vstupné napätie - ±1,999Uop(V),

Výkon - (2-9) Hz,

Spotreba prúdu - 1,8 mA

Napájacie napätie - 9V.

Obrázok 13.13. IS K572PV2 (a) a výstupné napätie na výstupe generátora (b)

Prevádzka integrovaného obvodu prebieha pod vplyvom hodinových impulzov f interného generátora impulzov v troch fázach:

V prvom stupni T1, ktorý trvá 4000 periód fty, je integrované napätie Ux,

V druhej fáze, ktorá trvá od 0 do 8 000 periód, fti je integrácia referenčného napätia U op a

V tretej fáze, ktorá trvá od 4000 do 12000 periód fty, sa operačný zosilňovač automaticky nastaví na nulu.

Celý cyklus konverzie trvá 16 000 cyklov.

Viackanálové ADC sú široko používané na prevod niekoľkých analógových hodnôt rovnakého typu. Takéto ADC zahŕňajú analógový prepínač a jeden z ADC diskutovaných vyššie.

Obrázok 13.14. Viackanálový ADC

Konverzia prebieha postupne parameter po parametri. Analógový prepínač striedavo spája všetky vstupné signály so vstupom ADC cez zosilňovač.

Pre pohodlie bude článok rozdelený na 2 časti.

I. časť

ADC alebo analógovo-digitálna konverzia.

V analógových zariadeniach má analógový zvuk podobu nepretržitého elektrického signálu, výpočtová technika zase pracuje iba s digitálnymi údajmi - preto je zvuk v počítači digitálny.

Myslím, že už máte nejaký zmätok medzi "zvukmi". Aby sme predišli nedorozumeniu, pouvažujme, čo je digitálny zvuk a ako sa analóg konvertuje „na digitálny“.

digitálny zvuk- spôsob znázornenia zvukového signálu pomocou diskrétnych číselných hodnôt jeho amplitúdy.

Ako obvykle, pokúsim sa všetko vysvetliť jednoduchším spôsobom. trochu sa opakujem.

Zvuková vlna je komplexná funkcia zobrazujúca závislosť jej amplitúdy od času.

Na digitalizáciu tejto vlny je potrebné ju opísať, pričom je potrebné zachovať diskrétnu hodnotu pre konkrétne body.

Hodnota amplitúdy zvukovej vlny sa musí merať v každom časovom bode a výsledná hodnota by sa mala zapísať ako čísla. Ale vzhľadom na nemožnosť stanovenia hodnoty amplitúdy s presnosťou 100%, musia byť zapísané v zaoblenej forme. Čo má za následok malé skreslenie pôvodného signálu. Inými slovami, dôjde k akejsi aproximácii tejto funkcie pozdĺž osi amplitúdy a časových súradníc.

Ako vidíte, proces digitalizácie signálu pozostáva z dvoch etáp.

1. Najprv - odber vzoriek (vzorkovanie)

2.Po druhé - kvantovanie.

Vzorkovanie- proces získavania hodnôt konvertovaného signálu v určitých časových intervaloch. Inými slovami, je to akoby „vzorkovanie“ signálu podľa daných hodnôt.

Kvantovanie- predstavuje proces nahradenia prijatých hodnôt amplitúdy signálu s maximálnou približnou presnosťou.

Ako je uvedené vyššie, pri prevode signálu je potrebné zaokrúhliť hodnoty kvôli nemožnosti zafixovať „skutočnú“ hodnotu amplitúdy s ideálnou (v skutočnosti nekonečnou) presnosťou. Počítače by na to potrebovali väčšie množstvo pamäte RAM (viac ako 1 TB) a môžete ju donekonečna upravovať, čo vo výsledku znamená vytvorenie pamäte RAM s nekonečným množstvom pamäte.

Presnosť zaokrúhľovania je ovplyvnená úrovňou kvantizácie (alebo bitovou hĺbkou kvantizácie). Čím väčší je počet úrovní, tým menšia je zaokrúhlená hodnota amplitúdy, čo má za následok menšiu chybu.

Na základe vyššie uvedeného už možno usúdiť, že digitalizácia signálu je fixácia amplitúdy zvukovej vlny v určitých časových intervaloch a záznam prijatej vlny s minimálnou chybou.

Je potrebné vyvodiť ďalší záver. Čím vyššia je vzorkovacia frekvencia a kvantizačná bitová hĺbka, tým presnejší je popis prijímaného signálu.

Kvalita priamo závisí od parametrov zvolených pre digitalizáciu. Sú to vzorkovacia frekvencia (vyjadrená v kHz) a bitová hĺbka (vyjadrená v bitoch).

Inými slovami, čím vyššia je bitová hĺbka a vzorkovacia frekvencia, tým lepší je signál a tým väčšie je množstvo digitalizovaných údajov. Preto tu treba hľadať „zlatú strednú cestu“ medzi hmotnosťou a kvalitou.

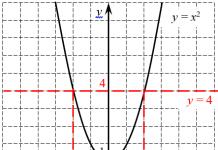

Kotelnikovova veta (v anglickej literatúre - Nyquist-Shannonova veta alebo vzorkovacia veta) uvádza, že ak má analógový signál konečné (obmedzenú šírku) spektrum, potom ho možno jedinečne a bez straty obnoviť z jeho diskrétnych vzoriek odobratých pomocou frekvencia striktne vyššia ako dvojnásobok hornej frekvencie.

V „preklade do normálnej ľudskej reči“ je na získanie čo najúplnejších informácií o zvuku, napríklad vo frekvenčnom rozsahu do 22 000 Hz, potrebný odber vzoriek s frekvenciou najmenej 44,1 kg.

To naznačuje, že nemá zmysel naháňať sa za vysokými vzorkovacími frekvenciami, pretože frekvencia 44,1 kHz pokrýva celý rozsah frekvencií, ktoré človek počuje, a dokonca aj o niečo vyššie.

Časť II

Digitálna-analógová konverzia.

Aby bolo možné počúvať zvuk po digitalizácii, musí byť prevedený späť na analógový.

Analógový signál môže byť spracovaný zosilňovačmi a inými analógovými zariadeniami a reprodukovaný reproduktormi.

Konvertuje digitálny signál na analógový - digitálno-analógový prevodník (DAC). Proces konverzie je inverzný postup ADC.

Moderné systémy prehrávajú a nahrávajú zvuk cez audio rozhranie, ktorého úlohou je vstup a výstup zvukovej informácie, t.j. Toto je zariadenie na konverziu analógového signálu na digitálny a naopak.

Činnosť zvukového rozhrania možno vysvetliť jednoduchšie.

Najprv vstupný analógový zvuk vstupuje do analógového vstupu (alebo mixéra), potom je odoslaný do ADC, ktorý ho kvantuje a vzorkuje. Výsledkom je digitálny audio signál, ktorý ide do počítača cez zbernicu a digitálny zvuk je získané.

Pri výstupe zvukovej informácie nastáva podobný proces, len v opačnom smere. Dátový tok prechádza cez DAC, ktorý premieňa čísla určujúce amplitúdu signálu na elektrický - analógový signál.

Schematicky to všetko vyzerá tak, ako je znázornené na obr

Chcem poznamenať, že ak je zvukové rozhranie vybavené rozhraním na výmenu digitálnych údajov, potom pri práci s digitálnym zvukom nie je zahrnutý žiadny z jeho analógových blokov - takže obídením prevodníkov zachováte zvuk takmer taký, aký je.

Článok popisuje zariadenie a princípy fungovania analógovo-digitálnych prevodníkov rôznych typov, ako aj ich hlavné charakteristiky uvedené výrobcami v dokumentácii.

Analógovo-digitálny prevodník (ADC) je jedným z najdôležitejších elektronických komponentov v meracích a testovacích zariadeniach. ADC konvertuje napätie (analógový signál) na kód, na ktorom mikroprocesor a softvér vykonávajú určité akcie. Aj keď pracujete iba s digitálnymi signálmi, s najväčšou pravdepodobnosťou používate ADC na vašom osciloskope, aby ste zistili ich analógové charakteristiky.

Existuje niekoľko základných typov architektúry ADC, hoci v rámci každého typu existuje aj veľa variácií. Rôzne typy meracích zariadení používajú rôzne typy ADC. Napríklad digitálny osciloskop používa vysokú vzorkovaciu frekvenciu, ale nevyžaduje vysoké rozlíšenie. Digitálne multimetre potrebujú väčšie rozlíšenie, ale môžete obetovať rýchlosť merania. Systémy zberu dát na všeobecné účely sa zvyčajne radia medzi osciloskopy a digitálne multimetre, pokiaľ ide o vzorkovaciu frekvenciu a rozlíšenie. Tento typ zariadenia používa postupnú aproximáciu ADC alebo sigma-delta ADC. Existujú aj paralelné ADC pre aplikácie, ktoré vyžadujú vysokorýchlostné spracovanie analógového signálu a integráciu ADC s vysokým rozlíšením a redukciou šumu.

Na obr. schopnosti hlavných architektúr ADC sú zobrazené v závislosti od rozlíšenia a vzorkovacej frekvencie.

Ryža. 1. Typy ADC - rozlíšenie v závislosti od vzorkovacej frekvencie

Paralelné ADC

Väčšina vysokorýchlostných osciloskopov a niektoré vysokofrekvenčné prístroje používajú paralelné ADC kvôli ich vysokej rýchlosti konverzie, ktorá môže dosiahnuť 5 Hz (5 x 10 9) vzoriek/s pre štandardné zariadenia a 20 Hz vzoriek/s pre originálne návrhy. Paralelné ADC majú zvyčajne rozlíšenie až 8 bitov, ale dostupné sú aj 10-bitové verzie.

Ryža. 2. Paralelná konverzia ADC

Ryža. 2 je znázornená zjednodušená bloková schéma 3-bitového paralelného ADC (pre prevodníky s vyšším rozlíšením je princíp činnosti rovnaký). Používa pole komparátorov, z ktorých každý porovnáva vstupné napätie s individuálnym referenčným napätím. Takéto referenčné napätie pre každý komparátor je vytvorené na vstavanom presnom odporovom deliči. Referencie napätia začínajú na polovici najnižšej významnej číslice (LSB) a zvyšujú sa s každým nasledujúcim komparátorom v prírastkoch V REF /2 3 . Výsledkom je, že 3-bitový ADC vyžaduje 2 3 -1 alebo sedem komparátorov. A napríklad pre 8-bitový paralelný ADC bude potrebných 255 (alebo (2 8 -1)) komparátorov.

Keď sa vstupné napätie zvyšuje, komparátory postupne nastavujú svoje výstupy na logickú jednotku namiesto logickej nuly, počnúc komparátorom zodpovedným za najmenej významný bit. Prevodník si môžete predstaviť ako ortuťový teplomer: so stúpajúcou teplotou stúpa ortuťový stĺpec. Na obr. 2, vstupné napätie klesne medzi V3 a V4, takže spodné 4 komparátory majú výstup "1" a tri horné komparátory majú výstup "0". Dekodér prevádza (2 3 -1) - bitové digitálne slovo z výstupov komparátorov na binárny 3-bitový kód.

Paralelné ADC sú primerane rýchle zariadenia, ale majú svoje nevýhody. Kvôli potrebe použiť veľký počet komparátorov spotrebúvajú paralelné ADC značnú energiu a nie sú praktické pre aplikácie napájané z batérie.

Keď je potrebné rozlíšenie 12, 14 alebo 16 bitov a nie je potrebná vysoká rýchlosť prevodu a určujúcimi faktormi nízka cena a nízka spotreba energie, zvyčajne sa používajú postupné aproximačné ADC. Tento typ ADC sa najčastejšie používa v rôznych prístrojoch a systémoch na zber údajov. V súčasnosti umožňujú postupné aproximačné ADC merať napätie s presnosťou až 16 bitov so vzorkovacou rýchlosťou od 100K (1x10 3) do 1M (1x10 6) vzoriek/s.

Ryža. 3 znázorňuje zjednodušený blokový diagram postupnej aproximácie ADC. Tento typ ADC je založený na špeciálnom registri postupnej aproximácie. Na začiatku cyklu prevodu sú všetky výstupy tohto registra nastavené na logickú 0, okrem prvého (najvyššieho) bitu. Toto generuje signál na výstupe interného digitálno-analógového prevodníka (DAC), ktorého hodnota sa rovná polovici vstupného rozsahu ADC. A výstup komparátora sa prepne do stavu, ktorý určuje rozdiel medzi signálom na výstupe DAC a nameraným vstupným napätím.

Ryža. 3. SAR ADC

Napríklad pre 8-bitový SAR ADC (obrázok 4) sú výstupy registra nastavené na „10000000“. Ak je vstupné napätie menšie ako polovica vstupného rozsahu ADC, potom výstup komparátora bude logická 0. To dáva pokyn postupnému aproximačnému registru, aby prepol svoje výstupy do stavu "01000000", čo zodpovedajúcim spôsobom zmení výstupné napätie. z DAC do komparátora. Ak by výstup komparátora zostal stále na "0", výstupy registra by sa prepli do stavu "00100000". Ale v tomto cykle konverzie je výstupné napätie DAC menšie ako vstupné napätie (obr. 4) a komparátor sa prepne do stavu logickej 1. To dáva pokyn postupnému aproximačnému registru, aby uložil "1" do druhého bitu. a aplikujte "1" na tretí bit. Opísaný operačný algoritmus sa potom znova opakuje až do poslednej číslice. Postupná aproximácia ADC teda vyžaduje jedny interné konverzné hodiny na bit alebo N hodín pre N-bitovú konverziu.

Ryža. 4. Konverzia postupných aproximácií na ADC

Činnosť postupnej aproximácie ADC má však zvláštnosť spojenú s prechodnými javmi vo vnútornom DAC. Teoreticky by napätie na výstupe DAC pre každý z N interných cyklov konverzie malo byť nastavené v rovnakom časovom období. Ale v skutočnosti je tento interval v prvých taktoch oveľa väčší ako v posledných. Preto je čas prevodu 16-bitového postupného aproximačného ADC viac ako dvojnásobkom času prevodu 8-bitového postupného aproximačného ADC.

Väčšina meraní často nevyžaduje ADC s rýchlosťou prevodu, ktorú poskytuje postupná aproximácia ADC, ale je potrebné vysoké rozlíšenie. Sigma-delta ADC môžu poskytnúť až 24 bitové rozlíšenie, ale majú nižšiu rýchlosť konverzie. Takže v sigma-delta ADC pri 16 bitoch môžete získať vzorkovaciu rýchlosť až 100 000 vzoriek/s a pri 24 bitoch táto frekvencia klesne na 1 000 vzoriek/s alebo menej, v závislosti od zariadenia.

Typicky sa sigma-delta ADC používajú v rôznych systémoch na zber údajov a v meracích zariadeniach (meranie tlaku, teploty, hmotnosti atď.), keď sa nevyžaduje vysoká vzorkovacia frekvencia a vyžaduje sa rozlíšenie viac ako 16 bitov.

Princíp činnosti sigma-delta ADC je ťažšie pochopiteľný. Táto architektúra patrí do triedy integrujúcich ADC. Hlavnou črtou sigma-delta ADC je však to, že vzorkovacia frekvencia, pri ktorej sa skutočne analyzuje úroveň napätia meraného signálu, výrazne prevyšuje vzorkovaciu frekvenciu na výstupe ADC (vzorkovacia frekvencia). Táto vzorkovacia frekvencia sa nazýva prevzorkovacia frekvencia. Napríklad sigma-delta ADC s rýchlosťou konverzie 100 000 vzoriek/s, ktorý používa rýchlosť prevzorkovania 128-krát rýchlejšiu, bude vzorkovať vstupný analógový signál rýchlosťou 12,8 miliónov vzoriek/s.

Bloková schéma sigma-delta ADC prvého rádu je znázornená na obr. 5. Analógový signál sa privádza do integrátora, ktorého výstupy sú pripojené ku komparátoru, ktorý je zase pripojený k 1-bitovému DAC v spätnoväzbovej slučke. Prostredníctvom série po sebe nasledujúcich iterácií integrátor, komparátor, DAC a sčítačka vytvárajú prúd sériových bitov, ktorý obsahuje informácie o veľkosti vstupného napätia.

Ryža. 5. Sigma-Delta ADC

Výsledná digitálna sekvencia je potom privedená do dolnopriepustného filtra na potlačenie komponentov nad Kotelnikovovou frekvenciou (polovičná vzorkovacia frekvencia ADC). Po odstránení vysokofrekvenčných komponentov nasledujúci uzol - decimátor - preriedi dáta. V ADC, o ktorom uvažujeme, decimátor ponechá 1 bit z každých 128 prijatých vo výstupnej digitálnej sekvencii.

Keďže interný digitálny dolnopriepustný filter v sigma-delta ADC je neoddeliteľnou súčasťou procesu konverzie, čas usadzovania dolnopriepustného filtra sa stáva faktorom, ktorý treba brať do úvahy pri preskakovaní vstupného signálu. Napríklad pri prepínaní vstupného multiplexora alebo pri prepínaní limitu merania zariadenia je potrebné počkať, kým prejde niekoľko vzoriek ADC, a až potom načítať správne výstupné údaje.

Ďalšou a veľmi dôležitou výhodou sigma-delta ADC je, že všetky jeho vnútorné jednotky môžu byť vyrobené integrálne na ploche jedného kremíkového čipu. To výrazne znižuje náklady na koncové zariadenia a zvyšuje stabilitu charakteristík ADC.

Integrácia ADC

A posledný typ ADC, o ktorom tu bude reč, je push-pull ADC. V digitálnych multimetroch sa spravidla používajú práve takéto ADC, pretože. tieto nástroje vyžadujú kombináciu vysokého rozlíšenia a vysokého potlačenia šumu. Myšlienka konverzie v takomto integrujúcom ADC je oveľa menej komplikovaná ako v sigma-delta ADC.

Obrázok 6 ukazuje, ako funguje push-pull ADC. Vstupný signál nabíja kondenzátor po pevne stanovenú dobu, čo je zvyčajne jeden cyklus sieťovej frekvencie (50 alebo 60 Hz) alebo jej násobok. Pri integrácii vstupného signálu v časovom úseku tohto trvania sa potlačí vysokofrekvenčný šum. Zároveň je eliminovaný vplyv nestability napätia sieťového zdroja na presnosť prevodu. Je to preto, že hodnota integrálu sínusového signálu je nulová, ak sa integrácia vykonáva v časovom intervale, ktorý je násobkom periódy sínusovej zmeny.

Ryža. 6. Integrácia ADC. Zelená farba ukazuje rušenie zo siete (1 perióda)

Na konci doby nabíjania ADC vybíja kondenzátor pevnou rýchlosťou, zatiaľ čo interné počítadlo počíta počet hodinových impulzov počas vybíjania kondenzátora. Dlhšiemu času vybíjania teda zodpovedá väčší stav merača a väčšie namerané napätie (obr. 6).

Push-pull ADC majú vysokú presnosť a vysoké rozlíšenie a majú tiež relatívne jednoduchú štruktúru. To umožňuje realizovať ich vo forme integrovaných obvodov. Hlavnou nevýhodou takýchto ADC je dlhý čas konverzie v dôsledku väzby integračnej periódy na trvanie periódy napájania. Napríklad pre 50 Hz zariadenia, vzorkovacia frekvencia push-pull ADC nepresahuje 25 vzoriek/s. Samozrejme, takéto ADC môžu pracovať aj s vyššou vzorkovacou frekvenciou, ale ako sa druhá zvyšuje, znižuje sa odolnosť voči šumu.

Špecifikácia ADC

Existujú všeobecné definície, ktoré sa bežne používajú vo vzťahu k analógovo-digitálnym prevodníkom. Špecifikácie uvedené v technickej dokumentácii výrobcov ADC však môžu pôsobiť dosť mätúco. Správny výber ADC, ktorý je optimálny z hľadiska jeho vlastností pre konkrétnu aplikáciu, vyžaduje presnú interpretáciu údajov uvedených v technickej dokumentácii.

Najčastejšie zmätené parametre sú rozlíšenie a presnosť, hoci tieto dve charakteristiky skutočného ADC spolu veľmi slabo súvisia. Rozlíšenie nie je totožné s presnosťou, 12-bitový ADC môže mať menšiu presnosť ako 8-bitový ADC. Pre ADC je rozlíšenie mierou toho, na koľko segmentov možno rozdeliť vstupný rozsah meraného analógového signálu (napríklad pre 8-bitový ADC je to 28 = 256 segmentov). Presnosť charakterizuje celkovú odchýlku výsledku prevodu od jeho ideálnej hodnoty pre dané vstupné napätie. To znamená, že rozlíšenie charakterizuje potenciálne schopnosti ADC a súbor parametrov presnosti určuje uskutočniteľnosť takejto potenciálnej schopnosti.

ADC konvertuje vstupný analógový signál na výstupný digitálny kód. Pre skutočné prevodníky vyrábané vo forme integrovaných obvodov nie je proces prevodu ideálny: je ovplyvnený tak technologickým šírením parametrov pri výrobe, ako aj rôznymi vonkajšími zásahmi. Preto je digitálny kód na výstupe ADC určený s chybou. Špecifikácia pre ADC označuje chyby, ktoré dáva samotný prevodník. Zvyčajne sa delia na statické a dynamické. Zároveň je to práve koncová aplikácia, ktorá určuje, ktoré charakteristiky ADC sa budú považovať za rozhodujúce, najdôležitejšie v každom konkrétnom prípade.

Statická chyba

Vo väčšine aplikácií sa ADC používa na meranie pomaly sa meniaceho nízkofrekvenčného signálu (napr. zo snímača teploty, tlakového snímača, tenzometra atď.), kde je vstupné napätie úmerné konštantnej fyzikálnej veličine. Tu hrá hlavnú úlohu chyba statického merania. V špecifikácii ADC je tento typ chyby definovaný aditívnou chybou (Offset), multiplikatívnou chybou (Full-Scale), diferenciálnou nelinearitou (DNL), integrálnou nelinearitou (INL) a kvantizačnou chybou. Týchto päť charakteristík vám umožní plne opísať statickú chybu ADC.

Ideálna prenosová odozva ADC

Prenosová charakteristika ADC je funkciou závislosti kódu na výstupe ADC od napätia na jeho vstupe. Takýto graf je po častiach lineárna funkcia 2N "krokov", kde N je bitová hĺbka ADC. Každý horizontálny segment tejto funkcie zodpovedá jednej z hodnôt výstupného kódu ADC (pozri obr. 7). Ak začiatky týchto horizontálnych segmentov spojíme čiarami (na hraniciach prechodu z jednej kódovej hodnoty na druhú), tak ideálnou prenosovou charakteristikou bude priamka prechádzajúca počiatkom.

Ryža. 7. Ideálna prenosová charakteristika 3-bitového ADC

Ryža. 7 znázorňuje ideálnu prenosovú charakteristiku pre 3-bitový ADC s bodmi prerušenia na hraniciach prechodu kódu. Výstupný kód nadobúda najmenšiu hodnotu (000b), keď je vstupný signál medzi 0 a 1/8 plného rozsahu (maximálna hodnota kódu tohto ADC). Všimnite si tiež, že ADC dosiahne kódovú hodnotu v plnej škále (111b) pri 7/8 plného rozsahu, nie pri plnom rozsahu. To. K prechodu na maximálnu hodnotu na výstupe nedochádza pri plnom napätí, ale pri hodnote menšej ako najmenšia významná číslica (LSB) ako je vstupné plné napätie. Prenosová charakteristika môže byť realizovaná s offsetom -1/2 LSB. To sa dosiahne posunutím prenosovej charakteristiky doľava, čím sa posunie kvantizačná chyba z -1...0 LSB na -1/2...+1/2 LSB.

Ryža. 8. Prenosová charakteristika 3-bitového ADC posunu o -1/2LSB

V dôsledku technologického rozšírenia parametrov pri výrobe integrovaných obvodov nemajú skutočné ADC ideálnu prenosovú charakteristiku. Odchýlky od ideálnej prenosovej charakteristiky určujú statickú chybu ADC a sú uvedené v technickej dokumentácii.

Ideálna prenosová charakteristika ADC prechádza počiatkom a prvý prechod kódu nastáva, keď sa dosiahne hodnota 1 LSB. Aditívnu chybu (chybu offsetu) môžeme definovať ako posun celej prenosovej charakteristiky doľava alebo doprava vzhľadom na os vstupného napätia, ako je znázornené na obr.9. Posun 1/2 LSB je teda zámerne zahrnutý do definície aditívnej chyby ADC.

Ryža. 9. Aditívna chyba (chyba posunu)

Multiplikačná chyba

Multiplikatívna chyba (chyba v celom rozsahu) je rozdiel medzi ideálnou a skutočnou prenosovou charakteristikou v bode maximálnej výstupnej hodnoty za podmienky nulovej aditívnej chyby (bez posunu). To sa prejavuje ako zmena sklonu prenosovej funkcie, čo je znázornené na obr. desať.

Ryža. 10. Multiplikatívna chyba (Chyba v plnom rozsahu)

Pre ideálnu prenosovú charakteristiku ADC by mala byť šírka každého "kroku" rovnaká. Rozdiel v dĺžke horizontálnych segmentov tejto po častiach lineárnej funkcie 2N "krokov" je diferenciálna nelinearita (DNL).

Hodnota najmenej významného bitu ADC je Vref/2N, kde Vref je referenčné napätie, N je rozlíšenie ADC. Rozdiel napätia medzi každým prechodom kódu sa musí rovnať hodnote LSB. Odchýlka tohto rozdielu od LSB je definovaná ako diferenciálna nelinearita. Na obrázku je to znázornené ako nerovnaké medzery medzi „krokmi“ kódu alebo ako „rozmazanie“ hraníc prechodu na prenosovej charakteristike ADC.

Ryža. 11. Diferenciálna nelinearita (DNL)

Integrálna nelinearita

Integrálna nelinearita (INL) je chyba, ktorá je spôsobená odchýlkou lineárnej funkcie prenosovej charakteristiky ADC od priamky, ako je znázornené na obr. 12. Prenosová funkcia s integrálnou nelinearitou sa zvyčajne aproximuje priamkou pomocou metódy najmenších štvorcov. Montážna priamka často jednoducho spája najmenšie a najväčšie hodnoty. Integrálna nelinearita je určená porovnaním napätí, pri ktorých dochádza k prechodom kódu. Pre ideálny ADC sa tieto prechody vyskytnú pri vstupných napätiach, ktoré sú presne násobky LSB. A pre skutočný prevodník môže byť takáto podmienka splnená s chybou. Rozdiel medzi „ideálnymi“ úrovňami napätia, pri ktorých dochádza k prechodu kódu, a ich skutočnými hodnotami je vyjadrený v jednotkách LSB a nazýva sa integrálna nelinearita.

Ryža. 12. Integrálna nelinearita (INL)

Chyba kvantizácie

Jedna z najvýznamnejších chýb pri meraniach ADC, kvantizačná chyba, je výsledkom samotného procesu konverzie. Chyba kvantovania je chyba spôsobená hodnotou kroku kvantovania a je definovaná ako? hodnota najnižšej významnej číslice (LSB). Nemožno ho vylúčiť pri analógovo-digitálnej konverzii, keďže je neoddeliteľnou súčasťou procesu konverzie, je určená rozlíšením ADC a nemení sa z ADC na ADC s rovnakým rozlíšením.

Dynamické charakteristiky

Dynamické charakteristiky ADC sa zvyčajne určujú pomocou spektrálnej analýzy z výsledkov vykonania rýchlej Fourierovej transformácie (FFT) na poli výstupných hodnôt ADC zodpovedajúcich nejakému testovaciemu vstupnému signálu.

Na obr. 13 je znázornený príklad frekvenčného spektra meraného signálu. Nulová harmonická zodpovedá základnej frekvencii vstupného signálu. Všetko ostatné je šum, ktorý zahŕňa harmonické skreslenie, tepelný šum, šum 1/f a kvantovací šum. Niektoré zložky šumu sú generované samotným ADC, niektoré môžu byť vstupom do ADC z externých obvodov. Napríklad harmonické skreslenie môže byť obsiahnuté v meranom signáli a súčasne generované ADC počas procesu prevodu.

Ryža. 13. Výsledok vykonania FFT na výstupných dátach ADC

Pomer signálu k šumu

Pomer signálu k šumu (SNR) je pomer efektívnej hodnoty vstupného signálu k efektívnej hodnote šumu (bez harmonického skreslenia), vyjadrený v decibeloch:

SNR(dB) = 20 log [ Vsignal(rms)/ Vnoise(rms) ]

Táto hodnota umožňuje určiť podiel šumu v meranom signáli vo vzťahu k užitočnému signálu.

Ryža. 14. SNR - Pomer signálu k šumu

Ryža. 15. FFT odráža harmonické skreslenie

Šum nameraný vo výpočte SNR nezahŕňa harmonické skreslenie, ale zahŕňa kvantovací šum. Pre ADC s určitým rozlíšením je to kvantizačný šum, ktorý obmedzuje možnosti prevodníka na teoreticky lepší pomer signálu k šumu, ktorý je definovaný ako:

SNR(db) = 6,02 N + 1,76,

kde N je rozlíšenie ADC.

Spektrum kvantizačného šumu ADC štandardných architektúr má rovnomerné rozdelenie frekvencií. Preto veľkosť tohto šumu nemožno znížiť zvýšením času konverzie a následným spriemerovaním výsledkov. Kvantizačný šum je možné znížiť iba meraním s väčším ADC.

Charakteristickým rysom sigma-delta ADC je, že jeho spektrum kvantizačného šumu je nerovnomerne rozložené na frekvencii - je posunuté smerom k vysokým frekvenciám. Predĺžením času merania (a podľa toho aj počtu vzoriek meraného signálu), akumuláciou a následným spriemerovaním získanej vzorky (dolnopriepustný filter) je teda možné získať výsledok merania s vyššou presnosťou. Prirodzene, v tomto prípade sa celkový čas konverzie zvýši.

Ďalšie zdroje šumu ADC zahŕňajú tepelný šum, šum 1/f a referenčný jitter.

Všeobecné harmonické skreslenie

Nelinearita výsledkov konverzie dát vedie k vzniku harmonického skreslenia. Takéto skreslenia sú pozorované ako „emisie“ vo frekvenčnom spektre pri párnych a nepárnych harmonických meraného signálu (obr. 15).

Toto skreslenie je definované ako celkové harmonické skreslenie (THD). Sú definované ako:

Miera harmonického skreslenia klesá pri vysokých frekvenciách do bodu, keď amplitúda harmonických klesá pod úroveň šumu. Ak teda analyzujeme príspevok harmonického skreslenia k výsledkom konverzie, možno to urobiť buď v celom frekvenčnom spektre, pri obmedzení amplitúdy harmonických pomocou úrovne šumu, alebo obmedzením šírky pásma na analýzu. Napríklad, ak má náš systém dolnopriepustný filter, potom nás vysoké frekvencie jednoducho nezaujímajú a vysokofrekvenčné harmonické nepodliehajú účtovaniu.

Pomer signálu k šumu a skreslenie

Pomer signálu k šumu a skreslenie (SiNAD) úplnejšie popisuje charakteristiky šumu ADC. SiNAD berie do úvahy množstvo šumu aj harmonického skreslenia vo vzťahu k užitočnému signálu. SiNAD sa vypočíta pomocou nasledujúceho vzorca:

Ryža. 16. Dynamický rozsah bez harmonických

Špecifikácia ADC uvedená v technickej dokumentácii pre mikroobvody pomáha pri rozumnom výbere prevodníka pre konkrétnu aplikáciu. Ako príklad zvážte špecifikáciu ADC integrovaného do nového mikrokontroléra C8051F064 vyrábaného spoločnosťou Silicon Laboratories.

Mikrokontrolér C8051F064

Kryštál C8051F064 je vysokorýchlostný 8-bitový mikrokontrolér na spoločné spracovanie analógových a digitálnych signálov s dvoma integrovanými 16-bitovými postupnými aproximačnými ADC. Vstavané ADC môžu pracovať v jednovodičovom a diferenciálnom režime s maximálnym výkonom až 1M vzoriek/s. V tabuľke sú uvedené hlavné charakteristiky ADC mikrokontroléra C8051F064. Ak chcete samostatne vyhodnotiť schopnosti digitálneho a analógového spracovania C8051F064, môžete použiť lacnú hodnotiacu súpravu C8051F064EK (obrázok 17). Súprava obsahuje hodnotiacu dosku založenú na C8051F064, USB kábel, dokumentáciu a softvér na testovanie analógových dynamických a statických charakteristík integrovaného vysoko presného 16-bitového ADC.

Tabuľka. V DD = 3,0 V, AV+ = 3,0 V, AVDD = 3,0 V, V REF = 2,50 V (REFBE=0), -40 až +85°, pokiaľ nie je uvedené inak

| možnosti | Podmienky | Typické | Max. | Jednotky |

| DC charakteristiky | ||||

| Bitová hĺbka | 16 | trocha | ||

| Integrálna nelinearita | jeden drôt | ±0,75 | ±2 | LSB |

| jeden drôt | ±0,5 | ±1 | LSB | |

| Zaručená monotónnosť | ± + 0,5 | LSB | ||

| Aditívna chyba (offset) | 0,1 | mV | ||

| Multiplikačná chyba | 0,008 | % F.S. | ||

| Zvýšenie teploty | 0,5 | ppm/°C | ||

| Dynamické charakteristiky (vzorkovacia frekvencia 1 Msps, AVDD, AV+ = 3,3 V) | ||||

| Signál/šum a skreslenie | Fin = 10 kHz, jeden vodič | 86 | dB | |

| Fin = 100 kHz, jeden vodič | 84 | dB | ||

| 89 | dB | |||

| 88 | dB | |||

| Všeobecné harmonické skreslenie | Fin = 10 kHz, jeden vodič | 96 | dB | |

| Fin = 100 kHz, jeden vodič | 84 | dB | ||

| Fin = rozdiel 10 kHz | 103 | dB | ||

| Fin = rozdiel 100 kHz | 93 | dB | ||

| Fin = 10 kHz, jeden vodič | 97 | dB | ||

| Fin = 100 kHz, jeden vodič | 88 | dB | ||

| Fin = rozdiel 10 kHz | 104 | dB | ||

| Fin = rozdiel 100 kHz | 99 | dB | ||

Ryža. 17. Hodnotiaca súprava C8051F064EK

Literatúra

- http://www.wbc-europe.com/en/services/pim_application_guide.html

- www.silabs.com

Wolfgang Reis (WBC GmbH)

Prednáška č.3

"Analógovo-digitálny a digitálno-analógový prevod".

V mikroprocesorových systémoch úlohu impulzného prvku plní analógovo-digitálny prevodník (ADC) a úlohu extrapolátora vykonáva digitálno-analógový prevodník (DAC).

Analógovo-digitálny prevod je previesť informácie obsiahnuté v analógovom signáli na digitálny kód . Digitálna konverzia na analógový navrhnutý na vykonávanie inverznej úlohy, t.j. previesť číslo reprezentované ako digitálny kód na ekvivalentný analógový signál.

ADC sú zvyčajne inštalované v spätnoväzbových obvodoch digitálnych riadiacich systémov na konverziu analógových spätnoväzbových signálov na kódy, ktoré vníma digitálna časť systému. To. ADC vykonávajú niekoľko funkcií, ako napríklad: časové vzorkovanie, kvantovanie úrovne, kódovanie. Zovšeobecnená bloková schéma ADC je znázornená na obr. 3.1.

Na vstup ADC sa privádza signál vo forme prúdu alebo napätia, ktorý je kvantovaný úrovňou počas procesu konverzie. Ideálna statická odozva 3-bitového ADC je znázornená na obrázku 3.2.

|

Vstupné signály môžu nadobúdať akúkoľvek hodnotu v rozsahu od - Umax až Umax a výstupy zodpovedajú ôsmim (2 3) diskrétnym úrovniam. Hodnota vstupného napätia, pri ktorej dochádza k prechodu z jednej hodnoty výstupného kódu ADC na inú susednú hodnotu, sa nazýva kódové prechodové napätie. Rozdiel medzi dvoma susednými hodnotami medzikódových prechodov sa nazýva kvantizačný krok alebo jednotka najnižšej významnej číslice (LSD).Východiskový bod konverznej charakteristiky sa nazýva bod definovaný hodnotou vstupného signálu, definovaný ako

(3.1),

kde U 0,1 je napätie prvého medzikódového prechodu, ULSB – krok kvantovania ( LSB - najmenej významný bit ). prevodu zodpovedá vstupné napätie, určené pomerom

![]() (3.2).

(3.2).

Rozsah vstupného napätia ADC, obmedzený hodnotami U 0,1 a UN-1,N volal rozsah vstupného napätia.

(3.3).

Rozsah vstupného napätia a hodnota LSB N -bitový pomer medzi linkami ADC a DAC

(3.4).

Napätie

(3.5)

volal plné napätie ( FSR-Full Scale Range ). Tento parameter je zvyčajne určený úrovňou výstupného signálu referenčného napätia pripojeného k ADC. Hodnota kvantizačného kroku alebo jednotka najmenej významného bitu, t.j. rovná sa

(3.6),

a jednotkovú hodnotu najvýznamnejšej číslice

![]() (3.7).

(3.7).

Ako je zrejmé z obr. 3.2, pri prepočte sa vyskytne chyba, ktorá nepresiahne polovicu hodnoty najmenej významnej číslice U LSB /2.

Existujú rôzne metódy analógovo-digitálnej konverzie, ktoré sa líšia presnosťou a rýchlosťou. Vo väčšine prípadov sú tieto vlastnosti navzájom antagonistické. V súčasnosti existujú také typy prevodníkov, ako sú ADC postupných aproximácií (bitové vyváženie), integrujúce ADC, paralelné ( Flash ) ADC, "sigma-delta" ADC atď.

Bloková schéma ADC postupných aproximácií je znázornená na obr.3.3.

Hlavnými prvkami zariadenia sú komparátor (K), digitálno-analógový prevodník (DAC) a logický riadiaci obvod. Princíp prevodu je založený na postupnom porovnávaní úrovne vstupného signálu s úrovňami signálu zodpovedajúcimi rôznym kombináciám výstupného kódu a vytvorení výsledného kódu na základe výsledkov porovnávania. Postupnosť porovnávaných kódov spĺňa pravidlo polovičného delenia. Na začiatku prevodu sa vstupný kód DAC nastaví do stavu, v ktorom sú všetky bity okrem najvyššieho bitu 0 a najvyšší bit je 1. Pri tejto kombinácii je napätie rovné polovici rozsahu vstupného napätia. generované na výstupe DAC. Toto napätie sa porovnáva so vstupným napätím na komparátore. Ak je vstupný signál väčší ako signál prichádzajúci z DAC, potom sa najvýznamnejší bit výstupného kódu nastaví na 1, inak sa nastaví na 0. V ďalšom cykle sa takto čiastočne vytvorený kód opäť privedie na vstup DAC, nasledujúci bit sa nastaví na jednotku a porovnanie sa zopakuje. Proces pokračuje, kým sa neporovná najmenej významný bit. To. formovať N - potrebný bitový výstupný kód N identické elementárne cykly porovnávania. To znamená, že za rovnakých okolností sa rýchlosť takéhoto ADC znižuje so zvyšovaním jeho kapacity. Vnútorné prvky postupnej aproximácie ADC (DAC a komparátor) musia mať presnosť lepšiu ako polovica LSB ADC.

Štrukturálny diagram rovnobežky ( Flash ) ADC je znázornené na obrázku 3.4.

V tomto prípade sa vstupné napätie použije na porovnanie so vstupmi rovnakého mena okamžite. N -1 porovnávače. Protiľahlé vstupy komparátorov prijímajú signály z vysoko presného deliča napätia, ktorý je pripojený k zdroju referenčného napätia. V tomto prípade sú napätia z výstupov deliča rovnomerne rozložené po celom rozsahu vstupného signálu. Prioritný kódovač generuje digitálny výstup zodpovedajúci najvyššiemu komparátoru s povoleným výstupom. To. poskytnúť N je potrebná bitová konverzia 2 N deliace odpory a 2 N -1 porovnávač. Toto je jedna z najrýchlejších metód konverzie. Pri veľkej kapacite si však vyžaduje veľké náklady na hardvér. Presnosť všetkých deliacich rezistorov a komparátorov by mala byť opäť lepšia ako polovica hodnoty najmenej významného bitu.

Bloková schéma ADC s dvojitou integráciou je znázornená na obrázku 3.5.

|

Hlavnými prvkami systému sú analógový spínač pozostávajúci z kľúčov SW 1, SW 2, SW 3, integrátor I, komparátor K a čítač C. Proces konverzie pozostáva z troch fáz (obr. 3.6).

|

V prvej fáze je kľúč zatvorený SW 1 a ostatné spínače sú otvorené. Prostredníctvom súkromného kľúča SW 1, vstupné napätie je privedené na integrátor, ktorý integruje vstupný signál v pevnom časovom intervale. Po tomto časovom intervale je úroveň výstupného signálu integrátora úmerná hodnote vstupného signálu. V druhej fáze transformácie je kľúč SW 1 sa otvorí a tlačidlo SW 2 je uzavretý a signál zo zdroja referenčného napätia je privedený na vstup integrátora. Kondenzátor integrátora sa vybíja z napätia nahromadeného v prvom intervale konverzie konštantnou rýchlosťou úmernou referenčnému napätiu. Tento stupeň trvá dovtedy, kým výstupné napätie integrátora neklesne na nulu, o čom svedčí výstupný signál komparátora, ktorý porovnáva signál integrátora s nulou. Trvanie druhého stupňa je úmerné vstupnému napätiu meniča. Počas celého druhého stupňa sú do počítadla privádzané vysokofrekvenčné impulzy s kalibrovanou frekvenciou. To. po druhom stupni sú digitálne hodnoty počítadla úmerné vstupnému napätiu. Touto metódou možno dosiahnuť veľmi dobrú presnosť bez kladenia vysokých nárokov na presnosť a stabilitu komponentov. Najmä stabilita kapacity integrátora nemusí byť vysoká, pretože cykly nabíjania a vybíjania prebiehajú rýchlosťou nepriamo úmernou kapacite. Okrem toho sú komparptorový drift a chyby offsetu kompenzované skutočnosťou, že každá fáza konverzie začína a končí pri rovnakom napätí. Na zlepšenie presnosti sa využíva tretí stupeň transformácie, kedy je vstup integrátora cez kľúč SW 3 je nulový signál. Pretože sa v tejto fáze používa rovnaký integrátor a komparátor, odčítanie hodnoty výstupnej chyby v nule od výsledku následného merania umožňuje kompenzovať chyby spojené s meraniami blízkymi nule. Prísne požiadavky nie sú kladené ani na frekvenciu hodinových impulzov dodávaných do počítadla, pretože z tých istých impulzov sa vytvorí pevný časový interval v prvom stupni premeny. Prísne požiadavky sú kladené len na vybíjací prúd, t.j. na zdroj referenčného napätia. Nevýhodou tohto spôsobu prevodu je nízka rýchlosť.

ADC sa vyznačujú množstvom parametrov, ktoré umožňujú realizovať výber konkrétneho zariadenia na základe požiadaviek na systém. Všetky parametre ADC možno rozdeliť do dvoch skupín: statické a dynamické. Prvý určuje charakteristiky presnosti zariadenia pri práci s konštantným alebo pomaly sa meniacim vstupným signálom a druhý charakterizuje rýchlosť zariadenia ako udržiavanie presnosti so zvyšujúcou sa frekvenciou vstupného signálu.

Úroveň kvantizácie ležiaca v blízkosti nuly vstupného signálu zodpovedá napätiam medzikódových prechodov –0,5 U LSB a 0,5 U LSB (prvý sa vyskytuje iba v prípade bipolárneho vstupného signálu). V skutočných zariadeniach sa však napätia týchto medzikódových prechodov môžu líšiť od týchto ideálnych hodnôt. Odchýlka skutočných úrovní týchto napätí medzikódových prechodov od ich ideálnych hodnôt sa nazýva bipolárna chyba posunutia nuly ( Bipolárna nulová chyba ) a unipolárna chyba posunutia nuly ( Chyba odsadenia nuly ), resp. Pri bipolárnych prevodných rozsahoch sa zvyčajne používa chyba nulového posunu a pri unipolárnych prevodoch sa používa unipolárna chyba posunu. Táto chyba vedie k paralelnému posunu reálnej transformačnej charakteristiky voči ideálnej charakteristike pozdĺž osi x (obr. 3.7).

|

Odchýlka úrovne vstupného signálu zodpovedajúca poslednému prechodu medzikódu od jeho ideálnej hodnoty U FSR -1,5 U LSB , sa volá chyba v plnom rozsahu ( Chyba v plnej mierke).

ADC prevodný faktor sa nazýva dotyčnica sklonu priamky vedenej cez začiatočný a koncový bod reálnej transformačnej charakteristiky. Rozdiel medzi skutočnou a ideálnou hodnotou konverzného faktora sa nazýva chyba konverzného faktora ( Chyba zisku ) (obr. 3.7).Zahŕňa chyby na koncoch stupnice, ale nezahŕňa nulové chyby stupnice. Pre unipolárny rozsah je definovaný ako rozdiel medzi chybou celej stupnice a unipolárnou chybou posunutia nuly a pre bipolárny rozsah je to rozdiel medzi chybou plnej stupnice a bipolárnou chybou posunutia nuly. V skutočnosti ide v každom prípade o odchýlku ideálnej vzdialenosti medzi posledným a prvým medzikódovým prechodom (rovná sa U FSR -2 U LSB ) od jeho skutočnej hodnoty.

Chyby nulového posunu a konverzného faktora je možné kompenzovať nastavením predzosilňovača ADC. K tomu musíte mať voltmeter s presnosťou najmenej 0,1 ULSB . Pre nezávislosť týchto dvoch chýb sa najprv opraví chyba nulového posunu a potom chyba transformačného koeficientu.Ak chcete opraviť chybu nulového posunu ADC, musíte:

1. Vstupné napätie nastavte presne na 0,5 U LSB;

2. Upravte offset predzosilňovača ADC, kým sa ADC neprepne do stavu 00…01.

Ak chcete opraviť chybu prevodného koeficientu, musíte:

1. Vstupné napätie nastavte presne na úroveň U FSR -1,5 U LSB ;

2. Upravte zosilnenie predzosilňovača ADC, kým sa ADC neprepne do stavu 11…1.

V dôsledku nedokonalosti prvkov obvodu ADC sa kroky v rôznych bodoch charakteristík ADC navzájom líšia veľkosťou a nie sú rovnaké. U LSB (obr. 3.8).

|

Odchýlka vzdialenosti medzi stredmi dvoch susedných reálnych kvantizačných krokov od ideálnej hodnoty kvantizačného kroku ULSB volal diferenciálna nelinearita (DNL - Diferenciálna nelinearita). Ak DNL väčší alebo rovný ULSB , potom môže mať ADC takzvané „chýbajúce kódy“ (obr. 3.3). To má za následok lokálnu prudkú zmenu prenosového koeficientu ADC, čo v uzavretých riadiacich systémoch môže viesť k strate stability.

Pre tie aplikácie, kde je dôležité udržiavať výstupný signál s danou presnosťou, je dôležité, aby výstupné kódy ADC čo najbližšie zodpovedali napätiam medzikódových prechodov. Nazýva sa maximálna odchýlka stredu kvantizačného kroku na skutočnej ADC charakteristike od linearizovanej charakteristiky integrálna nelinearita (INL - Integral Nonlinearity) resprelatívna presnosť (Relatívna presnosť) ADC (obrázok 3.9).

|

Linearizovaná charakteristika je nakreslená cez krajné body reálnej transformačnej charakteristiky po ich kalibrácii, t.j. eliminovali chyby nulového offsetu a konverzného faktora.

Je prakticky nemožné kompenzovať chyby v diferenciálnej a integrálnej nelinearite jednoduchými prostriedkami.

rozlíšenie ADC ( Rozhodnutie ) je prevrátená hodnota maximálneho počtu kombinácií kódov na výstupe ADC

(3.8).

Tento parameter určuje, akú minimálnu úroveň vstupného signálu (vo vzťahu k signálu s plnou amplitúdou) je ADC schopný akceptovať.

Presnosť a rozlíšenie sú dve nezávislé charakteristiky. Rozlíšenie hrá rozhodujúcu úlohu, keď je dôležité poskytnúť daný dynamický rozsah vstupného signálu. Presnosť je rozhodujúca, keď je potrebné udržiavať kontrolovanú hodnotu na danej úrovni s pevnou presnosťou.

Dynamický rozsah ADC (DR - Dynamic Range ) je pomer maximálnej vnímanej úrovne vstupného napätia k minimu, vyjadrený v dB

![]() (3.9).

(3.9).

Tento parameter určuje maximálne množstvo informácií, ktoré je ADC schopný preniesť. Takže pre 12-bitový ADC DR = 72 dB.

Charakteristiky skutočných ADC sa líšia od charakteristík ideálnych zariadení v dôsledku nedokonalosti prvkov skutočného zariadenia. Uvažujme o niektorých parametroch, ktoré charakterizujú skutočné ADC.

odstup signálu od šumu(SNR - pomer signálu k šumu ) je pomer efektívnej hodnoty vstupného sínusového signálu k efektívnej hodnote šumu, ktorý je definovaný ako súčet všetkých ostatných spektrálnych zložiek do polovice vzorkovacej frekvencie, s výnimkou jednosmernej zložky. Pre dokonalé N -bitový ADC, ktorý generuje iba kvantizačný šum SNR , vyjadrené v decibeloch, možno definovať ako

(3.10),

(3.10),

kde N - bitová hĺbka ADC. Takže pre 12-bitový ideálny ADC SNR = 74 dB. Táto hodnota je väčšia ako hodnota dynamického rozsahu rovnakého ADC. minimálna úroveň vnímaného signálu musí byť väčšia ako úroveň hluku. Tento vzorec berie do úvahy iba kvantizačný šum a neberie do úvahy iné zdroje hluku, ktoré existujú v skutočných ADC. Preto tie hodnoty SNR pre skutočné ADC je to spravidla menej ako ideálne. typická hodnota SNR pre skutočný 12-bitový ADC je 68-70 dB.

Ak má vstupný signál menší výkyv U FSR , potom je potrebné opraviť posledný vzorec

(3.11),

kde KOS je útlm vstupného signálu, vyjadrený v dB. Takže, ak má vstupný signál 12-bitového ADC amplitúdu 10-krát menšiu ako polovicu plného napätia, potom KOS = -20 dB a SNR=74dB - 20dB=54dB.

Skutočná hodnota SNR možno použiť na určenie efektívneho počtu bitov ADC( ENOB - Efektívny počet bitov ). Určuje sa podľa vzorca

![]() (3.12).

(3.12).

Tento indikátor môže charakterizovať skutočnú rozhodovaciu silu skutočného ADC. Takže 12-bitový ADC, ktorý má SNR =68dB pre signál s FOS=-20dB je v skutočnosti 7-bit ( ENOB = 7,68). hodnota ENOB silne závisí od frekvencie vstupného signálu, t.j. efektívna bitová hĺbka ADC klesá so zvyšujúcou sa frekvenciou.

Celkové harmonické skreslenie ( THD – celkové harmonické skreslenie ) je pomer súčtu efektívnych hodnôt všetkých vyšších harmonických k efektívnej hodnote základnej harmonickej

(3.13),

(3.13),

kde n zvyčajne limit na úrovni 6 alebo 9. Tento parameter charakterizuje úroveň harmonického skreslenia výstupného signálu ADC v porovnaní so vstupom. THD sa zvyšuje s frekvenciou vstupného signálu.

Plná výkonová šírka pásma ( FPBW - Full Power Bandwidth ) je maximálna vstupná frekvencia od špičky po špičku, pri ktorej sa amplitúda rekonštruovanej základnej frekvencie zníži o maximálne 3 dB. Keď sa frekvencia vstupného signálu zvyšuje, analógové obvody ADC už nemajú čas na spracovanie svojich zmien s danou presnosťou, čo vedie k zníženiu konverzného koeficientu ADC pri vysokých frekvenciách.

Čas vyrovnania (Nastavovať čas ) je čas potrebný na to, aby ADC dosiahol svoju nominálnu presnosť po privedení skokového signálu s amplitúdou rovnajúcou sa celému rozsahu vstupného signálu na jeho vstup. Tento parameter je obmedzený kvôli konečnej rýchlosti rôznych uzlov ADC.

V dôsledku rôznych druhov chýb je charakteristika skutočného ADC nelineárna. Ak je signál privedený na vstup zariadenia s nelinearitou, ktorého spektrum pozostáva z dvoch harmonických fa a f b , potom v spektre výstupného signálu takéhoto zariadenia budú okrem hlavných harmonických aj intermodulačné subharmonické s frekvenciami., kde m , n =1,2,3,… Subharmonické sú druhého rádu f a + f b , f a - f b , subharmoniky tretieho rádu sú 2 f a + f b , 2 f a - f b , f a +2 f b , f a -2 f b . Ak majú vstupné sínusoidy blízke frekvencie umiestnené blízko horného okraja šírky pásma, potom sú subharmoniky druhého rádu ďaleko od vstupných sínusoidov a nachádzajú sa v oblasti nižšej frekvencie, zatiaľ čo subharmonické subharmoniky tretieho rádu majú frekvencie blízke vstupným frekvenciám.

Faktor intermodulačného skreslenia ( Intermodulárne skreslenie ) je pomer súčtu efektívnych hodnôt intermodulačných subharmoník určitého rádu k súčtu efektívnych hodnôt základných harmonických, vyjadrený v dB

(3.14).

(3.14).

Akákoľvek metóda analógovo-digitálnej konverzie vyžaduje určitý čas na dokončenie. Pod čas konverzie ADC (Čas konverzie ) označuje časový interval od okamihu, keď analógový signál príde na vstup ADC, kým sa neobjaví zodpovedajúci výstupný kód. Ak sa vstupný signál ADC mení v čase, potom konečný čas konverzie ADC vedie k vzniku tzv. chyba clony(obr.3.10).

|

Signál spustenia konverzie prichádza v okamihu t0 , a momentálne sa zobrazí výstupný kód t1 . Počas tejto doby sa vstupný signál stihol zmeniť o hodnotuD U . Vzniká neistota: aká úroveň hodnoty vstupného signálu v rozsahu U 0 - U 0 + D U zodpovedá danému výstupnému kódu. Pre zachovanie presnosti prevodu na úrovni najmenej významnej číslice je potrebné, aby pri prevode nebola zmena hodnoty signálu na vstupe ADC väčšia ako hodnota najmenej významnej číslice.

![]() (3.15).

(3.15).

Zmenu úrovne signálu počas doby konverzie možno približne vypočítať ako

(3.16),

(3.16),

kde U - Vstupné napätie ADC, T c - čas konverzie. Dosadením (3.16) do (3.15) dostaneme

![]() (3.17).

(3.17).

Ak je vstupom sínusový signál s frekvenciou f

![]() (3.18),

(3.18),

potom bude jeho derivát

![]() (3.19).

(3.19).

Nadobudne maximálnu hodnotu, keď sa kosínus rovná 1. Dosadením (3.9) do (3.7) s prihliadnutím na to dostaneme

![]() , alebo

, alebo

(3.20)

Konečný čas konverzie ADC vedie k požiadavke obmedziť rýchlosť zmeny vstupného signálu. Aby sa znížila chyba clony atď. zoslabiť hranicu rýchlosti zmeny vstupného signálu ADC na vstupe prevodníka je nastavená na tzv. "zariadenie na uchovávanie vzoriek" (SHA) ( Jednotka sledovania/pridržania ). Zjednodušená schéma UVH je znázornená na obr. 3.11.

|

Toto zariadenie má dva režimy prevádzky: režim vzorkovania a režim blokovania. Režim vzorkovania zodpovedá zatvorenému stavu kľúča SW . V tomto režime výstupné napätie SHA opakuje svoje vstupné napätie. Režim uzamykania sa aktivuje príkazom, ktorý otvorí kľúč SW . V tomto prípade sa spojenie medzi vstupom a výstupom SHA preruší a výstupný signál sa udržiava na konštantnej úrovni zodpovedajúcej úrovni vstupného signálu v okamihu prijatia príkazu na uzamknutie v dôsledku náboja nahromadeného na zariadení. kondenzátor. Ak sa teda príkaz hold vydá tesne pred začiatkom konverzie ADC, výstupný signál SHA sa bude udržiavať na konštantnej úrovni počas celého času konverzie. Po dokončení konverzie sa SHA prepne späť do režimu vzorkovania. Fungovanie skutočného SHA sa trochu líši od ideálneho prípadu, ktorý bol popísaný (obr. 3.12).

|

![]() (3.21),

(3.21),

kde f je frekvencia vstupného signálu, t A je veľkosť neistoty clony.

V reálnom SHA nemôže výstupný signál zostať absolútne nezmenený počas konečného času konverzie. Kondenzátor sa bude postupne vybíjať malým vstupným prúdom výstupnej vyrovnávacej pamäte. Pre dodržanie požadovanej presnosti je potrebné, aby sa pri premene náboj kondenzátora nezmenil o viac ako 0,5 ULSB.

Digitálno-analógové prevodníky sa zvyčajne inštalujú na výstup mikroprocesorového systému na konverziu jeho výstupných kódov na analógový signál aplikovaný na objekt nepretržitého riadenia. Ideálna statická odozva 3-bitového DAC je znázornená na obrázku 3.13.

|

Charakteristický východiskový bod definovaný ako bod zodpovedajúci prvému (nulovému) vstupnému kódu U 00…0 . Charakteristický koncový bod definovaný ako bod zodpovedajúci poslednému vstupnému kódu U 11…1 . Definície rozsahu výstupného napätia, jednotky LSB, chyby nulového posunu a chyby prevodného pomeru sú podobné ako pri ADC.

Z hľadiska konštrukčného usporiadania má DAC oveľa menšiu škálu možností na stavbu meniča. Hlavnou štruktúrou DAC je tzv. "reťaz Schéma R -2 R“ (obr. 3.14).

Je ľahké ukázať, že vstupný prúd obvodu je I v = U REF / R a prúdy po sebe nasledujúcich článkov obvodu, resp Ja v /2, ja v /4, ja v /8 atď. Na premenu vstupného digitálneho kódu na výstupný prúd stačí na výstupnom bode prevodníka zozbierať všetky prúdy ramien zodpovedajúce jednotkám vo vstupnom kóde (obr. 3.15).

|

Ak je k výstupnému bodu meniča pripojený operačný zosilňovač, potom je možné výstupné napätie určiť ako

![]() (3.22),

(3.22),

kde K - zadajte digitálny kód, N - bitová hĺbka DAC.

Všetky existujúce DAC sú rozdelené do dvoch veľkých skupín: DAC s prúdovým výstupom a DAC s napäťovým výstupom. Rozdiel medzi nimi spočíva v absencii alebo prítomnosti koncového stupňa na operačnom zosilňovači v čipe DAC. Napäťové výstupné DAC sú kompletnejšie zariadenia a vyžadujú menej prídavných komponentov na prevádzku. Konečná fáza spolu s parametrami rebríkového obvodu však určuje dynamické a presné parametre DAC. Často je ťažké implementovať presný vysokorýchlostný operačný zosilňovač na rovnaký čip s DAC. Preto má väčšina vysokorýchlostných DAC prúdový výstup.

Diferenciálna nelinearita pre DAC je definovaný ako odchýlka vzdialenosti medzi dvoma susednými úrovňami analógového výstupného signálu od ideálnej hodnoty ULSB . Veľká hodnota diferenciálnej nelinearity môže spôsobiť, že DAC sa stane nemonotónnym. To znamená, že zvýšenie digitálneho kódu povedie k zníženiu výstupného signálu v niektorej časti charakteristiky (obr. 3.16). To môže viesť k nežiaducemu generovaniu v systéme.

|

Integrálna nelinearita pre DAC je definovaná ako najväčšia odchýlka úrovne analógového výstupného signálu od priamky vedenej cez body zodpovedajúce prvému a poslednému kódu po ich úprave.

Čas vyrovnania DAC je definovaný ako čas, ktorý trvá, kým sa výstupný signál DAC ustáli na danej úrovni s chybou nie väčšou ako 0,5 ULSB po zmene vstupného kódu z hodnoty 00…0 na hodnotu 11…1. Ak má DAC vstupné registre, tak určitá časť času ustálenia je spôsobená pevným oneskorením prechodu digitálnych signálov a iba zvyšná časť je spôsobená zotrvačnosťou samotného obvodu DAC. Preto sa čas ustálenia zvyčajne meria nie od okamihu, keď na vstup DAC príde nový kód, ale od okamihu, keď sa výstupný signál zodpovedajúci novému kódu začne meniť, až do okamihu, keď sa výstupný signál vytvorí s presnosťou 0,5U LSB (obr.3.17) .

|

V tomto prípade čas ustálenia určuje maximálnu vzorkovaciu frekvenciu DAC.

(3.23),

kde t S - doba vyrovnania.

Digitálne vstupné obvody DAC majú konečnú rýchlosť. Navyše rýchlosť šírenia signálov zodpovedajúcich rôznym bitom vstupného kódu nie je rovnaká v dôsledku šírenia parametrov prvkov a vlastností obvodu. V dôsledku toho sa ramená rebríkového obvodu DAC, keď príde nový kód, neprepínajú synchrónne, ale s určitým vzájomným oneskorením. To vedie k tomu, že v diagrame výstupného napätia DAC sa pri prechode z jednej ustálenej hodnoty na druhú pozorujú špičky rôznych amplitúd a smerov (obr. 3.18).

|

|

Podľa operačného algoritmu je DAC extrapolátor nultého rádu, ktorého frekvenčná odozva môže byť vyjadrená výrazom

(3.24),

(3.24),

kde w s - vzorkovacia frekvencia. Frekvenčná odozva DAC je znázornená na obrázku 3.20.

|

Ako je vidieť, pri frekvencii 0,5w s obnovený signál je zoslabený o 3,92 dB v porovnaní s nízkofrekvenčnými zložkami signálu. Dochádza teda k miernemu skresleniu spektra obnoveného signálu. Vo väčšine prípadov toto malé skreslenie výrazne neovplyvňuje parametre systému. Avšak v prípadoch, keď sa vyžaduje zvýšená linearita spektrálnych charakteristík systému (napríklad v systémoch na spracovanie zvuku), na vyrovnanie výsledného spektra na výstupe DAC je potrebné nainštalovať špeciálny regeneračný filter s frekvenciou odpoveď typu x/sin(x).