Convertidor D/A. .

Estos dispositivos son "conductores" entre cosa análoga y digital mundos de electricidad.

La conclusión es que sensores, motores, luces y muchos otros dispositivos utilizan Señal analoga, es decir, por ejemplo, un voltaje con un nivel de 0V a 12V, mientras que los FPGA digitales, los microcontroladores y los microcircuitos necesitan niveles de voltaje constantes, por ejemplo 0V y 5V, que son 0 y 1 lógicos respectivamente.

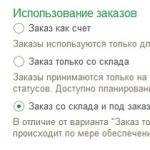

Ejemplo 1 CAD

Imagina que nos enfrentamos a la tarea de controlar el brillo de un LED:

- 10 niveles (graduaciones) Brillo LED

- tensión máxima vía LED 9V

- controlado por un microcontrolador y dos botones "+1 nivel de brillo", "-1 nivel de brillo"

Entonces, el LED funciona con un voltaje de 0 a 9V. Es fácil adivinar que 10 gradaciones de brillo son 10 niveles de voltaje que aplicamos al LED - 0V, 1V, ..., 9V

El microcontrolador emite 0V o 5V. Pero no 1V, 3V, 4V o 9V. Pero el microcontrolador tiene mucho lógico conclusiones a las que podemos conectar CAD en y convertir lógica en Señal analoga.

En convertidor de digital a analógico hay, por ejemplo, 4 pines de entrada para conectar señales lógicas y 2 pines para salida cosa análoga voltajes de 0 a 15V - conclusiones "+" y "-".

Aquí está tu trabajo CAD a: cuando servimos las 4 patas lógico 1, entonces el nivel de voltaje cosa análoga la señal de salida es máxima ( 15V en nuestro caso), cuando servimos 0 - el mínimo, es decir, 0V

Ahora lo más interesante. Cada terminal de entrada CAD pero hay un "peso" para la señal de salida. Por ejemplo, la salida superior "pesa" 8V (es decir, si aplica un 1 lógico solo a la primera salida, obtendremos 8V en la salida), siguiente por debajo de 4V, siguiente 2V y último bajo 1V. Ahora sume estos números y obtenga 15V.

Necesitamos obtener los niveles 0V, 1V, 2V, 3V, 4V, 5V, 6V, 7V, 8V y 9V.

Esto significa que las entradas CAD debe codificarse de acuerdo con la siguiente tabla

| Voltaje encendido cosa análoga toma de corriente | 0V | 1B | 2B | 3B | 4B | 5V | 6V | 7B | 8V | 9B |

| Entrada 1, peso 8V | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 |

| Entrada 1, peso 4V | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |

| Entrada 1, peso 2V | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 |

| Entrada 1, peso 1V | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

Los botones "+1 nivel de brillo", "-1 nivel de brillo" sumarán o restarán 1 unidad de la salida digital señal del microcontrolador. Esta señal se aplicará a las entradas CAD. Producción CAD se conectará al LED. ¡Misión cumplida!

Ejemplo 2. ADC

Conversor analógico a digitalfunciona al revés. Aplicamos un nivel de voltaje cambiante a la entrada, obtenemos lógica en la salida (pedacitos) +5V y 0V, o lógica 1 y 0

Configuremos la tarea para tomar lecturas del sensor de temperatura:

- el sensor muestra la temperatura de 0C a 30C

- a 0C el sensor emite 0V, a 30C emite 15V

- la señal debe ser recibida por el microcontrolador en forma digital (1 y 0 lógicos, voltaje + 5V y 0V)

ADC tiene dos pines de entrada para recibir una señal analógica con un voltaje, por ejemplo, de 0 a 15V y, en nuestro caso, 4 pines para la salida señal lógica digital. Es decir, una señal de código paralelo de cuatro bits.

Conectamos la salida de nuestro sensor a la entrada analógica ADC, y una salida digital de cuatro dígitos de ADC conectarse al microcontrolador. Y ya estamos aceptando lecturas del sensor en forma digital en el mikrik. Los datos en el proceso corresponderán a la siguiente tabla.

Un convertidor de analógico a digital es un dispositivo diseñado para convertir una cantidad física que cambia continuamente con el tiempo en valores de código digital equivalentes. Un valor analógico puede ser voltaje, corriente, desplazamiento angular, presión de gas, etc.

El proceso de conversión de analógico a digital implica la ejecución secuencial de las siguientes operaciones (Fig. 13.5):

Muestrear los valores del valor analógico original en algunos puntos de tiempo dados, es decir, muestreo de señal en el tiempo,

Cuantificación (redondeo del valor convertido a algunos valores conocidos) del valor del valor analógico obtenido en tiempos discretos por nivel,

Codificación: reemplazo de los valores cuánticos encontrados con algunos códigos numéricos.

Arroz. 13.5. El principio de la conversión de analógico a digital.

El error del ADC integrador está determinado principalmente por el cambio en la pendiente del voltaje de diente de sierra, que está determinado por la constante de tiempo del integrador RC (generador de voltaje de diente de sierra). Bajo la influencia de factores desestabilizadores externos, especialmente la temperatura, cambia la constante de tiempo y, por lo tanto, la pendiente de la tensión de diente de sierra, lo que conduce a errores de conversión significativos. Por lo tanto, en la actualidad, el principio de doble integración se utiliza para construir ADC integradores.

Principio de funcionamiento ADC de doble integración consiste en el hecho de que primero, durante un cierto intervalo de tiempo fijo T 1, se integra el valor convertido analógico U x, y luego se integra el voltaje de referencia (referencia) de polaridad opuesta U op. El intervalo de tiempo T 2 es proporcional al valor convertido U x .

Figura 13.11. Diagrama estructural del ADC de doble integración (a) y el diagrama de tiempo de su operación (b) De hecho, durante el intervalo de tiempo T 1, el voltaje a la salida del integrador cambia según una ley lineal:

Durante el intervalo de tiempo T 2, el voltaje de salida en la salida del integrador cambia de Uout.int.max a 0, es decir

Por lo tanto,

Así, el intervalo de tiempo T 2 depende de la constante T 1 /U op y de la variable U x y no depende de los parámetros del integrador. Esto se puede ver en el gráfico que se muestra en la figura 13.12.

Figura 13.12. El voltaje en la salida del integrador en una constante de tiempo τ 1 = R 1 * C 1 (1) y en τ 2 = R 2 * C 2 (1) El ADC de doble integración proporciona una alta precisión de conversión en condiciones de ruido industrial en un amplio rango de temperatura y es ampliamente utilizado en tecnología de medición y sistemas de control automatizados.

Por ejemplo, la base de todos los multímetros es el ADC de doble integración, fabricado en el chip K572PV2 o K572PV5. Los circuitos integrados son casi iguales, pero el primero controla los LED y el segundo controla los LCD.

El microcircuito K572PV2, junto con una fuente de voltaje de referencia, varias resistencias y capacitores, realiza las funciones de un ADC de doble integración con puesta a cero automática del amplificador operacional y determinación de la polaridad de la señal de entrada.

Principales parámetros técnicos de IS:

Profundidad de bits: 3,5 lugares decimales,

Impedancia de entrada - 50Mohm,

Voltaje de entrada - ±1.999Uop(V),

Rendimiento - (2-9) Hz,

Consumo de corriente - 1,8 mA

Tensión de alimentación - 9V.

Figura 13.13. IS K572PV2 (a) y voltaje de salida en la salida del generador (b)

El funcionamiento del IC se produce bajo la influencia de los pulsos de reloj f del generador de pulsos interno en tres etapas:

En la primera etapa T 1 , con una duración de 4000 periodos f ty, se integra la tensión U x,

En la segunda etapa, que dura de 0 a 8000 periodos, f ti es la integración de la tensión de referencia U op y

En la tercera etapa, que dura de 4000 a 12000 períodos f ty, el amplificador operacional se establece automáticamente en cero.

El ciclo de conversión completo toma 16,000 ciclos.

ADC multicanal son ampliamente utilizados para convertir varios valores analógicos del mismo tipo. Dichos ADC incluyen un interruptor analógico y uno de los ADC discutidos anteriormente.

Figura 13.14. ADC multicanal

La conversión ocurre secuencialmente parámetro por parámetro. El interruptor analógico conecta alternativamente todas las señales de entrada a la entrada ADC a través de un amplificador.

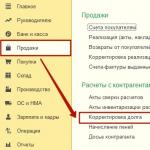

Por conveniencia, el artículo se dividirá en 2 partes.

Parte I

ADC o conversión de analógico a digital.

En los equipos analógicos, el sonido analógico tiene la forma de una señal eléctrica continua, la tecnología informática, a su vez, funciona solo con datos digitales: por lo tanto, el sonido en la computadora es digital.

Creo que ya tienes cierta confusión entre "sonidos". Para evitar malentendidos, consideremos qué es sonido digital y cómo lo analógico se convierte "a digital".

audio digital- un método para representar una señal de audio por medio de valores numéricos discretos de su amplitud.

Como siempre, intentaré explicarlo todo de una manera más sencilla. Repito un poco.

Una onda de sonido es una función compleja que representa la dependencia de su amplitud en el tiempo.

Para digitalizar esta onda, es necesario describirla, manteniendo un valor discreto a puntos específicos.

El valor de la amplitud de la onda de sonido debe medirse en cada punto de tiempo y el valor resultante debe escribirse como números. Pero, debido a la imposibilidad de fijar el valor de amplitud con una precisión del 100%, deben escribirse en forma redondeada. Lo que, en consecuencia, conlleva pequeñas distorsiones de la señal original. En otras palabras, habrá una especie de aproximación de esta función a lo largo de los ejes de coordenadas de amplitud y tiempo.

Como puede ver, el proceso de digitalización de señales consta de dos etapas.

1.Primero - muestreo (muestreo)

2.Segundo - cuantización.

Muestreo- el proceso de obtener los valores de la señal convertida en ciertos intervalos de tiempo. En otras palabras, es, por así decirlo, un "muestreo" de una señal según valores dados.

cuantización- representa el proceso de reemplazar los valores recibidos de la amplitud de la señal con la máxima precisión aproximada.

Como se mencionó anteriormente, al convertir una señal, es necesario redondear los valores debido a la imposibilidad de fijar el valor de amplitud "real" con una precisión ideal (de hecho, infinita). Para hacer esto, las computadoras necesitarían una mayor cantidad de RAM (más de 1 TB), y puedes refinarla indefinidamente, lo que, como resultado, implica la creación de RAM con una cantidad infinita de memoria.

La precisión de redondeo se ve afectada por el nivel de cuantificación (o la profundidad de bits de cuantificación). Cuanto mayor es el número de niveles, menor se redondea el valor de la amplitud, lo que, como resultado, da como resultado un error menor.

En base a lo anterior, ya se puede concluir que la digitalización de una señal es una fijación de la amplitud de una onda sonora en determinados intervalos de tiempo, y un registro de la recibida con un mínimo error.

Hay otra conclusión que sacar. Cuanto mayor sea la frecuencia de muestreo y la profundidad de bits de cuantificación, más precisa será la descripción de la señal recibida.

La calidad depende directamente de los parámetros elegidos para la digitalización. Estos son la frecuencia de muestreo (expresada en KHz) y la profundidad de bits (expresada en Bits).

En otras palabras, cuanto mayor sea la profundidad de bits y la frecuencia de muestreo, mejor se obtendrá la señal y mayor será la cantidad de datos digitalizados. Por lo tanto, aquí debe buscar la "media dorada" entre peso y calidad.

El teorema de Kotelnikov (en la literatura inglesa, el teorema de Nyquist-Shannon o el teorema de muestreo) establece que si una señal analógica tiene un espectro finito (de ancho limitado), entonces se puede restaurar de forma única y sin pérdida de sus muestras discretas tomadas con un frecuencia estrictamente mayor que el doble de la frecuencia superior.

En la “traducción al lenguaje humano normal”, para obtener la información más completa sobre el sonido, por ejemplo, en el rango de frecuencia hasta 22.000 Hz, se requiere un muestreo con una frecuencia de al menos 44,1 Kg.

Esto sugiere que no tiene sentido perseguir mucho las frecuencias de muestreo altas, ya que la frecuencia de 44,1 kHz cubre todo el rango de frecuencias que una persona puede escuchar, e incluso un poco más.

Parte II

Conversión de digital a analógico.

Para poder escuchar el sonido después de la digitalización, debe volver a convertirse a analógico.

La señal analógica puede ser procesada por amplificadores y otros dispositivos analógicos y reproducida por altavoces.

Convierte una señal digital a analógica: un convertidor de digital a analógico (DAC). El proceso de conversión es un procedimiento ADC inverso.

Los sistemas modernos reproducen y graban sonido a través de una interfaz de audio, cuya tarea es la entrada y salida de información de audio, es decir, Este es un dispositivo para convertir una señal analógica a digital y viceversa.

El funcionamiento de la interfaz de audio se puede explicar en términos más simples.

Primero, el sonido analógico de entrada ingresa a la entrada analógica (o mezclador), después de lo cual se envía al ADC, que lo cuantifica y lo muestrea. El resultado es una señal de audio digital que va a la computadora a través del bus y el sonido digital es obtenido.

Al emitir información de audio, ocurre un proceso similar, solo que en la dirección opuesta. El flujo de datos pasa a través del DAC, que convierte los números que determinan la amplitud de la señal en una señal analógica eléctrica.

Esquemáticamente, todo se ve como se muestra en la Fig. 1

Quiero señalar que si la interfaz de audio está equipada con una interfaz para el intercambio de datos digitales, entonces, cuando se trabaja con audio digital, ninguno de sus bloques analógicos está involucrado; por lo tanto, al pasar por alto los convertidores, mantendrá el sonido casi como está.

El artículo describe el dispositivo y los principios de funcionamiento de los convertidores de analógico a digital de varios tipos, así como sus principales características, indicadas por los fabricantes en la documentación.

El convertidor de analógico a digital (ADC) es uno de los componentes electrónicos más importantes en los equipos de medición y prueba. El ADC convierte el voltaje (señal analógica) en un código en el que el microprocesador y el software realizan ciertas acciones. Incluso si solo está trabajando con señales digitales, lo más probable es que esté utilizando un ADC en su osciloscopio para averiguar sus características analógicas.

Hay varios tipos básicos de arquitectura ADC, aunque también hay muchas variaciones dentro de cada tipo. Los diferentes tipos de equipos de medición utilizan diferentes tipos de ADC. Por ejemplo, un osciloscopio digital utiliza una tasa de muestreo alta pero no requiere una resolución alta. Los multímetros digitales necesitan más resolución, pero puede sacrificar la velocidad de medición. Los sistemas de adquisición de datos de uso general suelen clasificarse entre los osciloscopios y los multímetros digitales en términos de frecuencia de muestreo y resolución. Este tipo de equipo utiliza un ADC de aproximación sucesiva o un ADC sigma-delta. También hay ADC paralelos para aplicaciones que requieren procesamiento de señales analógicas de alta velocidad e integración de ADC con alta resolución y reducción de ruido.

En la figura 1. las capacidades de las principales arquitecturas ADC se muestran en función de la resolución y la frecuencia de muestreo.

Arroz. 1. Tipos de ADC: resolución según la frecuencia de muestreo

ADC paralelos

La mayoría de los osciloscopios de alta velocidad y algunos instrumentos de alta frecuencia utilizan ADC paralelos debido a su alta velocidad de conversión, que puede alcanzar 5 Hz (5 x 10 9) muestras/seg para dispositivos estándar y 20 Hz muestras/seg para diseños originales. Los ADC paralelos suelen tener una resolución de hasta 8 bits, pero también hay disponibles versiones de 10 bits.

Arroz. 2. Conversión paralela ADC

Arroz. 2 muestra un diagrama de bloques simplificado de un ADC paralelo de 3 bits (para convertidores con mayor resolución, el principio de funcionamiento es el mismo). Utiliza una matriz de comparadores, cada uno de los cuales compara el voltaje de entrada con un voltaje de referencia individual. Dicho voltaje de referencia para cada comparador se forma en el divisor resistivo de precisión incorporado. Las referencias de voltaje comienzan en la mitad del dígito menos significativo (LSB) y aumentan con cada comparador sucesivo en incrementos de V REF /2 3 . Como resultado, un ADC de 3 bits requiere 2 3 -1 o siete comparadores. Y, por ejemplo, para un ADC paralelo de 8 bits, se requerirán 255 (o (2 8 -1)) comparadores.

A medida que aumenta el voltaje de entrada, los comparadores establecen secuencialmente sus salidas en uno lógico en lugar de cero lógico, comenzando con el comparador responsable del bit menos significativo. Puede imaginar el convertidor como un termómetro de mercurio: a medida que aumenta la temperatura, aumenta la columna de mercurio. En la fig. 2, el voltaje de entrada cae entre V3 y V4, por lo que los 4 comparadores inferiores emiten "1" y los tres comparadores superiores emiten "0". El decodificador convierte (2 3 -1) - palabra digital de bits de las salidas de los comparadores en un código binario de 3 bits.

Los ADC paralelos son dispositivos razonablemente rápidos, pero tienen sus inconvenientes. Debido a la necesidad de usar una gran cantidad de comparadores, los ADC paralelos consumen una cantidad significativa de energía y no son prácticos para aplicaciones alimentadas por baterías.

Cuando se necesita una resolución de 12, 14 o 16 bits y no se requiere una alta velocidad de conversión, y el bajo precio y el bajo consumo de energía son los factores determinantes, se suelen utilizar ADC de aproximación sucesiva. Este tipo de ADC se usa más comúnmente en una variedad de sistemas de instrumentación y adquisición de datos. Actualmente, los ADC de aproximación sucesiva permiten medir voltaje con una precisión de hasta 16 bits con una tasa de muestreo de 100K (1x10 3) a 1M (1x10 6) muestras/seg.

Arroz. 3 muestra un diagrama de bloques simplificado de un ADC de aproximación sucesiva. Este tipo de ADC se basa en un registro especial de aproximación sucesiva. Al comienzo del ciclo de conversión, todas las salidas de este registro se establecen en 0 lógico, excepto el primer bit (el más alto). Esto genera una señal a la salida del convertidor digital a analógico (DAC) interno cuyo valor es igual a la mitad del rango de entrada del ADC. Y la salida del comparador cambia a un estado que determina la diferencia entre la señal en la salida del DAC y el voltaje de entrada medido.

Arroz. 3. ADC de SAR

Por ejemplo, para un ADC SAR de 8 bits (Figura 4), las salidas de registro se establecen en "10000000". Si el voltaje de entrada es inferior a la mitad del rango de entrada del ADC, entonces la salida del comparador será 0 lógico. Esto le indica al registro de aproximación sucesiva que cambie sus salidas al estado "01000000", lo que cambiará el voltaje de salida en consecuencia. del DAC al comparador. Si la salida del comparador aún permaneciera en "0", entonces las salidas del registro cambiarían al estado "00100000". Pero en este ciclo de conversión, el voltaje de salida del DAC es menor que el voltaje de entrada (Fig. 4), y el comparador cambia a un estado lógico 1. Esto le indica al registro de aproximación sucesiva que almacene un "1" en el segundo bit y aplicar un "1" al tercer bit. El algoritmo de operación descrito se repite luego de nuevo hasta el último dígito. Por lo tanto, un ADC de aproximación sucesiva requiere un reloj de conversión interno por bit, o N relojes para una conversión de N bits.

Arroz. 4. Conversión a ADC de aproximaciones sucesivas

Sin embargo, el funcionamiento del ADC de aproximación sucesiva tiene una peculiaridad asociada a los transitorios en el DAC interno. Teóricamente, el voltaje a la salida del DAC para cada uno de los N ciclos de conversión interna debería establecerse en el mismo período de tiempo. Pero, de hecho, este intervalo en los primeros compases es mucho mayor que en los últimos. Por lo tanto, el tiempo de conversión de un ADC de aproximación sucesiva de 16 bits es más del doble del tiempo de conversión de un ADC de aproximación sucesiva de 8 bits.

La mayoría de las mediciones a menudo no requieren un ADC con la velocidad de conversión que proporciona un ADC de aproximación sucesiva, pero se necesita una alta resolución. Los ADC Sigma-delta pueden proporcionar hasta 24 bits de resolución, pero son inferiores en velocidad de conversión. Por lo tanto, en un ADC sigma-delta a 16 bits, puede obtener una tasa de muestreo de hasta 100 000 muestras/seg, y a 24 bits esta frecuencia cae a 1000 muestras/seg o menos, según el dispositivo.

Por lo general, los ADC sigma-delta se utilizan en una variedad de sistemas de adquisición de datos y en equipos de medición (medición de presión, temperatura, peso, etc.) cuando no se requiere una tasa de muestreo alta y se requiere una resolución de más de 16 bits.

El principio de funcionamiento del ADC sigma-delta es más difícil de entender. Esta arquitectura pertenece a la clase de ADC integradores. Pero la característica principal del ADC sigma-delta es que la frecuencia de muestreo, a la que realmente se analiza el nivel de voltaje de la señal medida, supera significativamente la frecuencia de muestreo en la salida del ADC (frecuencia de muestreo). Esta frecuencia de muestreo se denomina frecuencia de remuestreo. Por ejemplo, un ADC sigma-delta con una tasa de conversión de 100 000 muestras/s, que utiliza una tasa de remuestreo 128 veces más rápida, muestreará la señal analógica de entrada a una tasa de 12,8 millones de muestras/s.

El diagrama de bloques del ADC sigma-delta de primer orden se muestra en la fig. 5. Se aplica una señal analógica a un integrador cuyas salidas están conectadas a un comparador, que a su vez está conectado a un DAC de 1 bit en un circuito de retroalimentación. Mediante una serie de iteraciones sucesivas, el integrador, el comparador, el DAC y el sumador producen un flujo de bits en serie que contiene información sobre la magnitud del voltaje de entrada.

Arroz. 5. ADC Sigma-Delta

La secuencia digital resultante luego se alimenta a un filtro de paso bajo para suprimir los componentes por encima de la frecuencia de Kotelnikov (la mitad de la frecuencia de muestreo del ADC). Después de eliminar los componentes de alta frecuencia, el siguiente nodo, el diezmador, reduce los datos. En el ADC que estamos considerando, el diezmador dejará 1 bit de cada 128 recibidos en la secuencia digital de salida.

Dado que el filtro de paso bajo digital interno en el ADC sigma-delta es una parte integral del proceso de conversión, el tiempo de establecimiento del filtro de paso bajo se convierte en un factor a considerar al saltar la señal de entrada. Por ejemplo, al cambiar el multiplexor de entrada o al cambiar el límite de medición del dispositivo, es necesario esperar hasta que hayan pasado varias muestras de ADC y solo entonces leer los datos de salida correctos.

Una ventaja adicional y muy importante del ADC sigma-delta es que todas sus unidades internas se pueden hacer integralmente en el área de un chip de silicio. Esto reduce significativamente el costo de los dispositivos finales y aumenta la estabilidad de las características del ADC.

Integración de ADC

Y el último tipo de ADC que se discutirá aquí es el ADC push-pull. En los multímetros digitales, por regla general, solo se usan tales ADC, porque. estos instrumentos requieren una combinación de alta resolución y alta supresión de ruido. La idea de conversión en un ADC integrador de este tipo es mucho menos complicada que en un ADC sigma-delta.

La Figura 6 muestra cómo funciona un ADC push-pull. La señal de entrada carga el condensador durante un período de tiempo fijo, que suele ser un ciclo de la frecuencia de la red (50 o 60 Hz) o un múltiplo de ella. Al integrar la señal de entrada durante un período de tiempo de esta duración, se suprime el ruido de alta frecuencia. Al mismo tiempo, se elimina la influencia de la inestabilidad de voltaje de la fuente de alimentación principal en la precisión de conversión. Esto se debe a que el valor de la integral de la señal sinusoidal es cero si la integración se realiza en un intervalo de tiempo múltiplo del período del cambio sinusoidal.

Arroz. 6. Integrando ADC. El color verde muestra interferencia de la red eléctrica (1 período)

Al final del tiempo de carga, el ADC descarga el capacitor a una tasa fija, mientras que un contador interno cuenta el número de pulsos de reloj durante la descarga del capacitor. Por lo tanto, un tiempo de descarga más largo corresponde a una lectura de medidor más grande y un voltaje medido más grande (Fig. 6).

Los ADC push-pull tienen alta precisión y alta resolución, y también tienen una estructura relativamente simple. Esto hace posible implementarlos en forma de circuitos integrados. La principal desventaja de tales ADC es el largo tiempo de conversión, debido a la vinculación del período de integración con la duración del período de suministro de energía. Por ejemplo, para equipos de 50 Hz, la frecuencia de muestreo del ADC push-pull no supera las 25 muestras/seg. Por supuesto, tales ADC también pueden funcionar con una frecuencia de muestreo más alta, pero a medida que aumenta esta última, la inmunidad al ruido disminuye.

Especificación ADC

Hay definiciones generales que se usan comúnmente en relación con los convertidores de analógico a digital. Sin embargo, las especificaciones dadas en la documentación técnica de los fabricantes de ADC pueden parecer bastante confusas. La elección correcta del ADC óptimo en términos de combinación de sus características para una aplicación particular requiere una interpretación precisa de los datos proporcionados en la documentación técnica.

Los parámetros que más se confunden son la resolución y la precisión, aunque estas dos características de un ADC real están muy poco relacionadas. La resolución no es idéntica a la precisión, un ADC de 12 bits puede tener menos precisión que un ADC de 8 bits. Para un ADC, la resolución es una medida de cuántos segmentos se puede dividir el rango de entrada de la señal analógica medida (por ejemplo, para un ADC de 8 bits, esto es 28 = 256 segmentos). La precisión caracteriza la desviación total del resultado de conversión de su valor ideal para un voltaje de entrada dado. Es decir, la resolución caracteriza las capacidades potenciales del ADC y el conjunto de parámetros de precisión determina la viabilidad de dicha capacidad potencial.

El ADC convierte la señal analógica de entrada en un código digital de salida. Para convertidores reales fabricados en forma de circuitos integrados, el proceso de conversión no es ideal: se ve afectado tanto por la dispersión tecnológica de los parámetros durante la producción como por diversas interferencias externas. Por lo tanto, el código digital en la salida del ADC se determina con un error. La especificación para el ADC indica los errores que da el propio convertidor. Suelen dividirse en estáticos y dinámicos. Al mismo tiempo, es la aplicación final la que determina qué características del ADC se considerarán determinantes, las más importantes en cada caso concreto.

error estático

En la mayoría de las aplicaciones, un ADC se usa para medir una señal de baja frecuencia que varía lentamente (por ejemplo, de un sensor de temperatura, sensor de presión, medidor de tensión, etc.) donde el voltaje de entrada es proporcional a una cantidad física constante. Aquí el papel principal lo juega el error de medición estático. En la especificación ADC, este tipo de error se define por error aditivo (Offset), error multiplicativo (Full-Scale), no linealidad diferencial (DNL), no linealidad integral (INL) y error de cuantificación. Estas cinco características le permiten describir completamente el error estático del ADC.

Respuesta de transferencia ideal de ADC

La característica de transferencia de un ADC es una función de la dependencia del código en la salida del ADC del voltaje en su entrada. Tal gráfico es una función lineal por partes de 2N "pasos", donde N es la profundidad de bits del ADC. Cada segmento horizontal de esta función corresponde a uno de los valores del código de salida del ADC (ver Fig. 7). Si conectamos los comienzos de estos segmentos horizontales con líneas (en los límites de la transición de un valor de código a otro), entonces la característica de transferencia ideal será una línea recta que pase por el origen.

Arroz. 7. Característica de transferencia ideal de ADC de 3 bits

Arroz. 7 ilustra la característica de transferencia ideal para un ADC de 3 bits con puntos de interrupción en los límites de transición de código. El código de salida toma el valor más pequeño (000b) cuando la señal de entrada está entre 0 y 1/8 de escala completa (el valor máximo de código de este ADC). También tenga en cuenta que el ADC alcanzará el valor de código de escala completa (111b) a 7/8 de escala completa, no a escala completa. Ese. La transición al valor máximo en la salida no ocurre a la tensión de escala completa, sino a un valor menor que el dígito menos significativo (LSB) que la tensión de escala completa de entrada. La característica de transferencia se puede implementar con un desplazamiento LSB de -1/2. Esto se logra desplazando la característica de transferencia hacia la izquierda, lo que desplaza el error de cuantificación de -1...0 LSB a -1/2...+1/2 LSB.

Arroz. 8. Característica de transferencia de un ADC de 3 bits compensado por -1/2LSB

Debido a la difusión tecnológica de los parámetros en la fabricación de circuitos integrados, los ADC reales no tienen una característica de transferencia ideal. Las desviaciones de la característica de transferencia ideal determinan el error estático del ADC y se indican en la documentación técnica.

La característica de transferencia ideal del ADC cruza el origen y la primera transición de código ocurre cuando se alcanza el valor de 1 LSB. El error aditivo (error de compensación) se puede definir como el desplazamiento de toda la característica de transferencia hacia la izquierda o hacia la derecha en relación con el eje del voltaje de entrada, como se muestra en la Fig. 9. Por lo tanto, un desplazamiento de 1/2 LSB se incluye deliberadamente en la definición de error de ADC aditivo.

Arroz. 9. Error aditivo (Error de compensación)

error multiplicativo

El error multiplicativo (error de escala completa) es la diferencia entre las características de transferencia ideales y reales en el punto de valor de salida máximo bajo la condición de error aditivo cero (sin compensación). Esto se manifiesta como un cambio en la pendiente de la función de transferencia, que se ilustra en la Fig. diez.

Arroz. 10. Error multiplicativo (error de escala completa)

Para una característica de transferencia ADC ideal, el ancho de cada "paso" debe ser el mismo. La diferencia en la longitud de los segmentos horizontales de esta función lineal por partes de 2N "pasos" es una no linealidad diferencial (DNL).

El valor del bit menos significativo del ADC es Vref/2N, donde Vref es el voltaje de referencia, N es la resolución del ADC. La diferencia de voltaje entre cada transición de código debe ser igual al valor de LSB. La desviación de esta diferencia de LSB se define como no linealidad diferencial. En la figura, esto se muestra como espacios desiguales entre los "pasos" del código, o como "difuminación" de los límites de transición en la característica de transferencia del ADC.

Arroz. 11. No linealidad diferencial (DNL)

No linealidad integral

La no linealidad integral (INL) es un error causado por la desviación de la función lineal de la característica de transferencia del ADC de una línea recta, como se muestra en la Fig. 12. Por lo general, una función de transferencia con una no linealidad integral se aproxima mediante una línea recta utilizando el método de mínimos cuadrados. A menudo, la línea recta de ajuste simplemente conecta los valores más pequeños y más grandes. La no linealidad integral se determina comparando los voltajes a los que ocurren las transiciones de código. Para un ADC ideal, estas transiciones ocurrirán en voltajes de entrada que son exactamente múltiplos de LSB. Y para un convertidor real, tal condición puede cumplirse con un error. La diferencia entre los niveles de tensión "ideales" en los que se produce la transición de código y sus valores reales se expresa en unidades LSB y se denomina no linealidad integral.

Arroz. 12. No linealidad integral (INL)

error de cuantización

Uno de los componentes de error más importantes en las mediciones de ADC, el error de cuantificación, es el resultado del propio proceso de conversión. El error de cuantificación es el error causado por el valor del paso de cuantificación y se define como? valor del dígito menos significativo (LSB). No se puede excluir en las conversiones de analógico a digital, ya que es una parte integral del proceso de conversión, está determinada por la resolución del ADC y no cambia de ADC a ADC con igual resolución.

Características dinámicas

Las características dinámicas de un ADC generalmente se determinan mediante análisis espectral, a partir de los resultados de realizar una transformada rápida de Fourier (FFT) en una matriz de valores de salida de ADC correspondientes a alguna señal de entrada de prueba.

En la fig. 13 muestra un ejemplo del espectro de frecuencia de la señal medida. El armónico cero corresponde a la frecuencia fundamental de la señal de entrada. Todo lo demás es ruido, que incluye distorsión armónica, ruido térmico, ruido 1/f y ruido de cuantificación. Algunos componentes de ruido son generados por el propio ADC, algunos pueden ingresar al ADC desde circuitos externos. La distorsión armónica, por ejemplo, puede estar contenida en la señal medida y ser generada simultáneamente por el ADC durante el proceso de conversión.

Arroz. 13. El resultado de la ejecución de FFT en los datos de salida del ADC

Relación señal-ruido

La relación señal-ruido (SNR) es la relación entre el valor RMS de la señal de entrada y el valor RMS del ruido (excluyendo la distorsión armónica), expresada en decibelios:

SNR(dB) = 20 log [ Vseñal(rms)/ Vruido(rms) ]

Este valor le permite determinar la proporción de ruido en la señal medida en relación con la señal útil.

Arroz. 14. SNR - Relación señal/ruido

Arroz. 15. FFT refleja la distorsión armónica

El ruido medido en el cálculo de SNR no incluye la distorsión armónica, pero sí el ruido de cuantificación. Para un ADC con una resolución determinada, es el ruido de cuantificación el que limita las capacidades del convertidor a una relación señal/ruido teóricamente mejor, que se define como:

SNR(db) = 6,02 N + 1,76,

donde N es la resolución del ADC.

El espectro de ruido de cuantificación del ADC de las arquitecturas estándar tiene una distribución de frecuencia uniforme. Por lo tanto, la magnitud de este ruido no puede reducirse aumentando el tiempo de conversión y luego promediando los resultados. El ruido de cuantificación solo se puede reducir realizando mediciones con un ADC más grande.

Una característica del ADC sigma-delta es que su espectro de ruido de cuantificación se distribuye de manera desigual en la frecuencia: se desplaza hacia las frecuencias altas. Por lo tanto, aumentando el tiempo de medición (y, en consecuencia, el número de muestras de la señal medida), acumulando y luego promediando la muestra obtenida (filtro de paso bajo), se puede obtener un resultado de medición con mayor precisión. Naturalmente, en este caso, el tiempo total de conversión aumentará.

Otras fuentes de ruido ADC incluyen el ruido térmico, el ruido 1/f y la fluctuación de fase de referencia.

Distorsión armónica general

La no linealidad en los resultados de la conversión de datos conduce a la aparición de distorsión armónica. Tales distorsiones se observan como "emisiones" en el espectro de frecuencia en armónicos pares e impares de la señal medida (Fig. 15).

Esta distorsión se define como distorsión armónica total (THD). Se definen como:

La cantidad de distorsión armónica disminuye a altas frecuencias hasta el punto en que la amplitud de los armónicos se vuelve menor que el nivel de ruido. Por lo tanto, si analizamos la contribución de la distorsión armónica a los resultados de la conversión, esto se puede hacer en todo el espectro de frecuencias, limitando la amplitud de los armónicos por el nivel de ruido, o limitando el ancho de banda para el análisis. Por ejemplo, si nuestro sistema tiene un filtro de paso bajo, simplemente no estamos interesados en las frecuencias altas y los armónicos de alta frecuencia no están sujetos a contabilidad.

Relación señal-ruido y distorsión

La relación señal-ruido y distorsión (SiNAD) describe más completamente las características de ruido de un ADC. SiNAD tiene en cuenta la cantidad de ruido y distorsión armónica en relación con la señal útil. SiNAD se calcula utilizando la siguiente fórmula:

Arroz. 16. Rango dinámico libre de armónicos

La especificación ADC, dada en la documentación técnica para microcircuitos, ayuda a seleccionar razonablemente un convertidor para una aplicación particular. Como ejemplo, considere la especificación del ADC integrado en el nuevo microcontrolador C8051F064 fabricado por Silicon Laboratories.

Microcontrolador C8051F064

El cristal C8051F064 es un microcontrolador de 8 bits de alta velocidad para el procesamiento conjunto de señales analógicas y digitales con dos ADC integrados de aproximación sucesiva de 16 bits. Los ADC incorporados pueden operar en modos diferenciales y de un solo cable con un rendimiento máximo de hasta 1 millón de muestras/seg. La tabla muestra las principales características del ADC del microcontrolador C8051F064. Para evaluar las capacidades de procesamiento digital y analógico del C8051F064 por su cuenta, puede usar el económico kit de evaluación C8051F064EK (Figura 17). El kit incluye una placa de evaluación basada en C8051F064, un cable USB, documentación y software para probar las características estáticas y dinámicas analógicas de un ADC integrado de 16 bits de alta precisión.

Mesa. V DD = 3,0 V, AV+ = 3,0 V, AVDD = 3,0 V, V REF = 2,50 V (REFBE=0), -40 a +85° a menos que se indique lo contrario

| Opciones | Condiciones | Típico | máx. | Unidades |

| Características de CC | ||||

| Profundidad de bits | 16 | poco | ||

| No linealidad integral | un solo cable | ±0,75 | ±2 | LSB |

| un solo cable | ±0,5 | ±1 | LSB | |

| Monotonicidad garantizada | ±+0.5 | LSB | ||

| Error aditivo (compensación) | 0,1 | mV | ||

| error multiplicativo | 0,008 | % fondo de escala | ||

| Ganancia de temperatura | 0,5 | ppm/ºC | ||

| Características dinámicas (frecuencia de muestreo 1 Msps, AVDD, AV+ = 3,3 V) | ||||

| Señal/ruido y distorsión | Aleta = 10 kHz, un solo cable | 86 | dB | |

| Fin = 100 kHz, un solo cable | 84 | dB | ||

| 89 | dB | |||

| 88 | dB | |||

| Distorsión armónica general | Aleta = 10 kHz, un solo cable | 96 | dB | |

| Fin = 100 kHz, un solo cable | 84 | dB | ||

| Aleta = diferencial de 10 kHz | 103 | dB | ||

| Aleta = diferencial de 100 kHz | 93 | dB | ||

| Aleta = 10 kHz, un solo cable | 97 | dB | ||

| Fin = 100 kHz, un solo cable | 88 | dB | ||

| Aleta = diferencial de 10 kHz | 104 | dB | ||

| Aleta = diferencial de 100 kHz | 99 | dB | ||

Arroz. 17. Kit de evaluación C8051F064EK

Literatura

- http://www.wbc-europe.com/en/services/pim_application_guide.html

- www.silabs.com

Wolfgang Reis (WBC GmbH)

Conferencia #3

"Conversión de analógico a digital y de digital a analógico".

En los sistemas de microprocesador, el papel de un elemento de pulso lo realiza un convertidor de analógico a digital (ADC), y el papel de un extrapolador lo realiza un convertidor de digital a analógico (DAC).

Conversión de analógico a digital es convertir la información contenida en la señal analógica en un código digital . Conversión de digital a analógico diseñado para realizar la tarea inversa, es decir, convertir un número representado como un código digital en una señal analógica equivalente.

Los ADC generalmente se instalan en los circuitos de retroalimentación de los sistemas de control digital para convertir las señales de retroalimentación analógicas en códigos que son percibidos por la parte digital del sistema. Ese. Los ADC realizan varias funciones, tales como: muestreo temporal, cuantificación de nivel, codificación. En la figura 3.1 se muestra un diagrama de bloques generalizado del ADC.

Se aplica una señal en forma de corriente o voltaje a la entrada del ADC, que se cuantifica por nivel durante el proceso de conversión. La respuesta estática ideal de un ADC de 3 bits se muestra en la Figura 3.2.

|

Las señales de entrada pueden tomar cualquier valor en el rango de − Umáx a Umáx , y las salidas corresponden a ocho (2 3) niveles discretos. El valor del voltaje de entrada en el que hay una transición de un valor del código de salida del ADC a otro valor adyacente se llama tensión de transición de código. La diferencia entre dos valores adyacentes de transiciones de intercodificación se llama paso de cuantización o unidad de dígito menos significativo (LSD).Punto de partida de la característica de conversión se denomina punto definido por el valor de la señal de entrada, definida como

(3.1),

donde U 0.1 es el voltaje de la primera transición de intercodificación, ULSB – paso de cuantificación ( LSB - Bit menos significativo ). la conversión corresponde a la tensión de entrada, determinada por la relación

![]() (3.2).

(3.2).

Rango de voltaje de entrada ADC, limitado por valores U 0.1 y U N-1,N llamado rango de voltaje de entrada.

(3.3).

Rango de voltaje de entrada y valor LSB norte Relación de enlaces ADC y DAC de bits

(3.4).

Voltaje

(3.5)

llamado voltaje de escala completa ( Rango de escala completa FSR ). Por lo general, este parámetro está determinado por el nivel de la señal de salida de la referencia de voltaje conectada al ADC. El valor del paso de cuantificación o la unidad del bit menos significativo, es decir es igual a

(3.6),

y el valor unitario del dígito más significativo

![]() (3.7).

(3.7).

Como se puede ver en la Fig. 3.2, durante la conversión ocurre un error que no excede la mitad del valor del dígito menos significativo U LSB /2.

Existen varios métodos de conversión de analógico a digital, que difieren en precisión y velocidad. En la mayoría de los casos, estas características son antagónicas entre sí. En la actualidad, tipos de convertidores como ADC de aproximaciones sucesivas (balanceo bit a bit), ADC integradores, paralelo ( Flash ) ADC, ADC "sigma-delta", etc.

El diagrama de bloques del ADC de aproximaciones sucesivas se muestra en la Fig.3.3.

Los elementos principales del dispositivo son un comparador (K), un convertidor de digital a analógico (DAC) y un circuito de control lógico. El principio de conversión se basa en la comparación secuencial del nivel de la señal de entrada con los niveles de la señal correspondientes a varias combinaciones del código de salida y la formación del código resultante en base a los resultados de las comparaciones. La secuencia de códigos comparados satisface la regla de la división a medias. Al comienzo de la conversión, el código de entrada del DAC se establece en un estado en el que todos los bits, excepto el bit más alto, son 0, y el bit más alto es 1. Con esta combinación, se obtiene un voltaje igual a la mitad del rango de voltaje de entrada. generado en la salida DAC. Este voltaje se compara con el voltaje de entrada en el comparador. Si la señal de entrada es mayor que la señal proveniente del DAC, entonces el bit más significativo del código de salida se establece en 1; de lo contrario, se restablece en 0. En el siguiente ciclo, el código formado parcialmente de esta manera se vuelve a alimentar a la entrada DAC, el siguiente bit se establece en uno y se repite la comparación. El proceso continúa hasta que se compara el bit menos significativo. Ese. formar norte - código de salida de bit necesario norte ciclos elementales idénticos de comparación. Esto significa que, en igualdad de condiciones, la velocidad de dicho ADC disminuye con un aumento en su capacidad. Los elementos internos del ADC de aproximación sucesiva (DAC y comparador) deben tener una precisión superior a la mitad del LSB del ADC.

Diagrama estructural de un paralelo ( Flash ) ADC se muestra en la Figura 3.4.

En este caso, el voltaje de entrada se aplica inmediatamente para compararlo con las entradas del mismo nombre. norte -1 comparadores. Las entradas opuestas de los comparadores reciben señales de un divisor de voltaje de alta precisión, que está conectado a una fuente de voltaje de referencia. En este caso, los voltajes de las salidas del divisor se distribuyen uniformemente a lo largo de todo el rango de la señal de entrada. El codificador de prioridad genera una salida digital correspondiente al comparador más alto con la salida habilitada. Ese. Para proveer norte -conversión de bits necesaria 2 norte resistencias divisoras y 2 norte -1 comparador. Este es uno de los métodos de conversión más rápidos. Sin embargo, con una gran capacidad, requiere grandes costos de hardware. La precisión de todas las resistencias divisoras y comparadores debería ser nuevamente mejor que la mitad del valor del bit menos significativo.

El diagrama de bloques del ADC de doble integración se muestra en la Figura 3.5.

|

Los elementos principales del sistema son un interruptor analógico, que consta de teclas SW 1, SW 2, SW 3, integrador I, comparador K y contador C. El proceso de conversión consta de tres fases (Fig. 3.6).

|

La llave se cierra en la primera fase SUDOESTE 1, y el resto de interruptores están abiertos. A través de una clave privada SUDOESTE 1, se aplica un voltaje de entrada a un integrador que integra la señal de entrada durante un intervalo de tiempo fijo. Después de este intervalo de tiempo, el nivel de la señal de salida del integrador es proporcional al valor de la señal de entrada. En la segunda etapa de la transformación, la clave SUDOESTE 1 se abre y la llave SUDOESTE 2 se cierra y se aplica una señal de la fuente de voltaje de referencia a la entrada del integrador. El capacitor integrador se descarga del voltaje acumulado en el primer intervalo de conversión a una tasa constante proporcional al voltaje de referencia. Esta etapa dura hasta que el voltaje de salida del integrador cae a cero, como lo demuestra la señal de salida del comparador que compara la señal del integrador con cero. La duración de la segunda etapa es proporcional a la tensión de entrada del convertidor. Durante toda la segunda etapa, se alimentan al contador pulsos de alta frecuencia con una frecuencia calibrada. Ese. después de la segunda etapa, las lecturas digitales del contador son proporcionales al voltaje de entrada. Con este método, se puede lograr una muy buena precisión sin imponer grandes exigencias a la precisión y estabilidad de los componentes. En particular, la estabilidad de la capacitancia del integrador puede no ser alta, ya que los ciclos de carga y descarga ocurren a una tasa inversamente proporcional a la capacitancia. Además, los errores de deriva y compensación del comparador se compensan haciendo que cada paso de conversión comience y finalice con el mismo voltaje. Para mejorar la precisión, se utiliza la tercera etapa de la transformación, cuando la entrada del integrador a través de la clave SUDOESTE 3 es una señal cero. Dado que en esta etapa se utilizan el mismo integrador y comparador, restar el valor del error de salida en cero del resultado de la medición posterior permite compensar los errores asociados con las mediciones cercanas a cero. No se imponen requisitos estrictos ni siquiera sobre la frecuencia de los pulsos de reloj suministrados al contador, porque un intervalo de tiempo fijo en la primera etapa de la conversión se forma a partir de los mismos pulsos. Se imponen requisitos estrictos solo a la corriente de descarga, es decir, a la fuente de voltaje de referencia. La desventaja de este método de conversión es la baja velocidad.

Los ADC se caracterizan por una serie de parámetros que permiten implementar la elección de un dispositivo específico en función de los requisitos del sistema. Todos los parámetros ADC se pueden dividir en dos grupos: estáticos y dinámicos. Los primeros determinan las características de precisión del dispositivo cuando se trabaja con una señal de entrada constante o que cambia lentamente, y los segundos caracterizan la velocidad del dispositivo para mantener la precisión al aumentar la frecuencia de la señal de entrada.

El nivel de cuantificación que se encuentra en la vecindad de cero de la señal de entrada corresponde a los voltajes de las transiciones de intercodificación –0.5 UL LSB y 0,5 U LSB (lo primero ocurre solo en el caso de una señal de entrada bipolar). Sin embargo, en dispositivos reales, los voltajes de estas transiciones de intercodificación pueden diferir de estos valores ideales. La desviación de los niveles reales de estos voltajes de transiciones de intercodificación de sus valores ideales se llama error de compensación cero bipolar ( Error cero bipolar ) y error de desplazamiento cero unipolar ( Error de compensación cero ) respectivamente. Con los rangos bipolares, las conversiones suelen utilizar un error de compensación cero y, con los unipolares, un error de compensación unipolar. Este error conduce a un desplazamiento paralelo de la característica de transformación real en relación con la característica ideal a lo largo del eje de abscisas (Fig. 3.7).

|

Desviación del nivel de la señal de entrada correspondiente a la última transición de intercodificación de su valor ideal U FSR -1.5 U LSB , se llama error de escala completa ( Error de escala completa).

factor de conversión ADC se denomina tangente de la pendiente de la recta trazada por los puntos inicial y final de la característica de transformación real. La diferencia entre el valor real e ideal del factor de conversión se llama error del factor de conversión ( Error de ganancia ) (Fig. 3.7) Incluye errores en los extremos de la escala, pero no incluye cero errores de la escala. Para un rango unipolar se define como la diferencia entre el error de escala completa y el error de compensación cero unipolar, y para un rango bipolar es la diferencia entre el error de escala completa y el error de compensación cero bipolar. De hecho, en cualquier caso, esta es la desviación de la distancia ideal entre la última y la primera transición de intercodificación (igual a U FSR-2 U LSB ) de su valor real.

Los errores de compensación cero y factor de conversión se pueden compensar ajustando el preamplificador ADC. Para hacer esto, debe tener un voltímetro con una precisión de al menos 0.1 ULSB . Para la independencia de estos dos errores, primero se corrige el error de desplazamiento cero y luego el error del coeficiente de transformada.Para corregir el error de compensación cero del ADC, debe:

1. Establezca el voltaje de entrada exactamente en 0.5 UL LSB;

2. Ajuste la compensación del preamplificador del ADC hasta que el ADC cambie al estado 00…01.

Para corregir el error del coeficiente de conversión, debe:

1. Ajuste el voltaje de entrada exactamente al nivel UFSR-1,5 UL LSB;

2. Ajuste la ganancia del preamplificador ADC hasta que el ADC cambie al estado 11…1.

Debido a la imperfección de los elementos del circuito ADC, los pasos en diferentes puntos de las características del ADC difieren entre sí en magnitud y no son iguales. UL LSB (Fig. 3.8).

|

Desviación de la distancia entre los puntos medios de dos pasos de cuantificación reales adyacentes del valor ideal del paso de cuantificación ULSB llamado no linealidad diferencial (DNL - No linealidad diferencial). Si DNL mayor que o igual ULSB , entonces el ADC puede tener los llamados "códigos faltantes" (Fig. 3.3). Esto implica un cambio local brusco en el coeficiente de transmisión ADC, que en sistemas de control cerrados puede conducir a la pérdida de estabilidad.

Para aquellas aplicaciones en las que es importante mantener la señal de salida con una precisión determinada, es importante que los códigos de salida del ADC coincidan lo más posible con los voltajes de las transiciones de intercodificación. La desviación máxima del centro del paso de cuantificación en la característica ADC real de la característica linealizada se llama no linealidad integral (INL - No linealidad integral) oexactitud relativa (Precisión relativa) ADC (Figura 3.9).

|

La característica linealizada se dibuja a través de los puntos extremos de la característica de transformación real, después de haber sido calibrados, es decir eliminó errores de compensación cero y factor de conversión.

Es prácticamente imposible compensar los errores de no linealidad diferencial e integral por medios simples.

resolución ADC ( Resolución ) es el recíproco del número máximo de combinaciones de códigos en la salida del ADC

(3.8).

Este parámetro determina qué nivel mínimo de señal de entrada (en relación con la señal de amplitud total) puede aceptar el ADC.

La precisión y la resolución son dos características independientes. La resolución juega un papel decisivo cuando es importante proporcionar un rango dinámico dado de la señal de entrada. La precisión es decisiva cuando se requiere mantener el valor controlado en un nivel dado con una precisión fija.

rango dinámico ADC (DR - Rango dinámico ) es la relación entre el nivel de tensión de entrada máximo percibido y el mínimo, expresado en dB

![]() (3.9).

(3.9).

Este parámetro determina la cantidad máxima de información que el ADC es capaz de transmitir. Entonces, para un ADC de 12 bits DR=72dB.

Las características de los ADC reales difieren de las características de los dispositivos ideales debido a la imperfección de los elementos de un dispositivo real. Consideremos algunos parámetros que caracterizan los ADC reales.

relación señal-ruido(SNR - Relación señal/ruido ) es la relación entre el valor rms de la señal sinusoidal de entrada y el valor rms del ruido, que se define como la suma de todos los demás componentes espectrales hasta la mitad de la frecuencia de muestreo, excluyendo el componente de CC. para el perfecto norte -bit ADC que genera solo ruido de cuantificación SNR , expresado en decibelios, se puede definir como

(3.10),

(3.10),

donde N - profundidad de bits del ADC. Entonces, para un ADC ideal de 12 bits SNR =74 dB. Este valor es mayor que el valor del rango dinámico del mismo ADC. el nivel mínimo de la señal percibida debe ser mayor que el nivel de ruido. Esta fórmula tiene en cuenta solo el ruido de cuantificación y no tiene en cuenta otras fuentes de ruido que existen en los ADC reales. Por lo tanto, los valores SNR para los ADC reales, por regla general, es menos que ideal. valor típico SNR para un ADC real de 12 bits es de 68-70 dB.

Si la señal de entrada tiene una oscilación menor U FSR , entonces la última fórmula necesita ser corregida

(3.11),

donde KOS es la atenuación de la señal de entrada, expresada en dB. Entonces, si la señal de entrada de un ADC de 12 bits tiene una amplitud 10 veces menor que la mitad del voltaje de escala completa, entonces KOS = -20 dB y SNR=74dB - 20dB=54dB.

Valor real SNR se puede utilizar para determinar el número efectivo de bits ADC( ENOB - Número efectivo de bits ). Está determinado por la fórmula

![]() (3.12).

(3.12).

Este indicador puede caracterizar el poder de decisión real de un ADC real. Entonces, un ADC de 12 bits, que tiene SNR =68dB para una señal con FOS=-20dB es en realidad de 7 bits ( ENOB=7,68). valor ENOB depende en gran medida de la frecuencia de la señal de entrada, es decir, la profundidad de bits efectiva del ADC disminuye con el aumento de la frecuencia.

Distorsión armónica total ( THD - Distorsión armónica total ) es la relación de la suma de los valores RMS de todos los armónicos superiores al valor RMS del armónico fundamental

(3.13),

(3.13),

donde n suele limitarse al nivel 6 o 9. Este parámetro caracteriza el nivel de distorsión armónica de la señal de salida del ADC en comparación con la entrada. THD aumenta con la frecuencia de la señal de entrada.

Ancho de banda de potencia completa ( FPBW - Ancho de banda de máxima potencia ) es la frecuencia máxima de entrada pico a pico en la que la amplitud de la fundamental reconstruida se reduce en no más de 3 dB. A medida que aumenta la frecuencia de la señal de entrada, los circuitos ADC analógicos ya no tienen tiempo para calcular sus cambios con una precisión dada, lo que conduce a una disminución en el coeficiente de conversión ADC a altas frecuencias.

Tiempo de estabilización (Ajuste de tiempo ) es el tiempo requerido para que el ADC alcance su precisión nominal después de que se haya aplicado a su entrada una señal de paso con una amplitud igual al rango completo de la señal de entrada. Este parámetro está limitado debido a la velocidad finita de varios nodos ADC.

Debido a varios tipos de errores, la característica de un ADC real es no lineal. Si se aplica una señal a la entrada de un dispositivo con no linealidades, cuyo espectro consta de dos armónicos fa y fb , entonces en el espectro de la señal de salida de dicho dispositivo, además de los armónicos fundamentales, habrá subarmónicos de intermodulación con frecuencias, donde m , n =1,2,3,… Los subarmónicos de segundo orden son fa + f segundo , fa - f segundo , los subarmónicos de tercer orden son 2 fa + f segundo , 2 fa - f segundo , fa +2 f segundo , fa -2 f segundo . Si las sinusoides de entrada tienen frecuencias cercanas ubicadas cerca del borde superior del ancho de banda, entonces los subarmónicos de segundo orden están lejos de las sinusoides de entrada y están ubicados en la región de frecuencia más baja, mientras que los subarmónicos de tercer orden tienen frecuencias cercanas a las frecuencias de entrada.

Factor de distorsión de intermodulación ( Distorsión intermodular ) es la relación de la suma de los valores RMS de los subarmónicos de intermodulación de un orden determinado a la suma de los valores RMS de los armónicos fundamentales, expresado en dB

(3.14).

(3.14).

Cualquier método de conversión de analógico a digital requiere un tiempo finito para completarse. Por debajo tiempo de conversión ADC ( Tiempo de conversión ) se refiere al intervalo de tiempo desde que llega la señal analógica a la entrada del ADC hasta que aparece el código de salida correspondiente. Si la señal de entrada del ADC cambia en el tiempo, entonces el tiempo de conversión final del ADC conduce a la aparición de los llamados. error de apertura(fig. 3.10).

|

La señal de inicio de conversión llega en el momento t0 , y el código de salida aparece en el momento t1 . Durante este tiempo, la señal de entrada logró cambiar por el valorD tu . Surge la incertidumbre: qué nivel del valor de la señal de entrada en el rango U 0 - U 0 + D tu corresponde al código de salida dado. Para mantener la precisión de la conversión al nivel del dígito menos significativo, es necesario que durante la conversión el cambio en el valor de la señal en la entrada del ADC no sea mayor que el valor del dígito menos significativo.

![]() (3.15).

(3.15).

El cambio en el nivel de la señal durante el tiempo de conversión se puede calcular aproximadamente como

(3.16),

(3.16),

donde estas – Voltaje de entrada ADC, T c - tiempo de conversión. Sustituyendo (3.16) en (3.15) obtenemos

![]() (3.17).

(3.17).

Si la entrada es una señal sinusoidal con una frecuencia F

![]() (3.18),

(3.18),

entonces su derivada será

![]() (3.19).

(3.19).

Toma un valor máximo cuando el coseno es igual a 1. Sustituyendo (3.9) en (3.7) teniendo esto en cuenta, obtenemos

![]() , o

, o

(3.20)

El tiempo de conversión finito del ADC conduce al requisito de limitar la tasa de cambio de la señal de entrada. Para reducir el error de apertura, etc. debilitar el límite en la tasa de cambio de la señal de entrada ADC en la entrada del convertidor se establece en el llamado. "dispositivo de retención de muestras" (SHA) ( Unidad de seguimiento/retención ). En la Fig. 3.11 se muestra un diagrama simplificado de la UVH.

|

Este dispositivo tiene dos modos de funcionamiento: modo de muestreo y modo de enganche. El modo de muestreo corresponde al estado cerrado de la llave. SUDOESTE . En este modo, el voltaje de salida SHA repite su voltaje de entrada. El modo de bloqueo se activa mediante un comando que abre la llave SUDOESTE . En este caso, la conexión entre la entrada y la salida del SHA se interrumpe y la señal de salida se mantiene a un nivel constante correspondiente al nivel de la señal de entrada en el momento en que se recibe el comando de bloqueo debido a la carga acumulada en el condensador. Por lo tanto, si se emite un comando de espera justo antes del inicio de la conversión ADC, la señal de salida SHA se mantendrá a un nivel constante durante todo el tiempo de conversión. Una vez completada la conversión, el SHA vuelve a cambiar al modo de muestreo. El funcionamiento de un SHA real es algo diferente del caso ideal, que se describió (Fig. 3.12).

|

![]() (3.21),

(3.21),

donde f es la frecuencia de la señal de entrada, t un es la magnitud de la incertidumbre de apertura.

En SHA real, la señal de salida no puede permanecer absolutamente sin cambios durante un tiempo de conversión finito. El condensador se descargará gradualmente por la pequeña corriente de entrada del búfer de salida. Para mantener la precisión requerida, es necesario que durante la conversión la carga del capacitor no cambie en más de 0.5 ULSB.

Convertidores de digital a analógico generalmente se instalan en la salida de un sistema de microprocesador para convertir sus códigos de salida en una señal analógica suministrada a un objeto de control continuo. La respuesta estática ideal de un DAC de 3 bits se muestra en la Figura 3.13.

|

Punto de partida característico definido como el punto correspondiente al primer (cero) código de entrada tu 00…0 . Punto final característico definido como el punto correspondiente al último código de entrada 11…1 . Las definiciones del rango de voltaje de salida, unidad LSB, error de compensación cero, error de relación de conversión son similares a las del ADC.

Desde el punto de vista de la organización estructural, el DAC tiene una variedad mucho menor de opciones para construir un convertidor. La estructura principal del DAC es la llamada. "cadena Esquema R -2 R” (Fig. 3.14).

Es fácil demostrar que la corriente de entrada del circuito es Yo en = U REF / R , y las corrientes de los sucesivos eslabones del circuito, respectivamente yo en /2, yo en /4, yo en /8 etc Para convertir el código digital de entrada en una corriente de salida, basta con recoger todas las corrientes de los brazos correspondientes a unidades en el código de entrada en el punto de salida del convertidor (Fig. 3.15).

|

Si se conecta un amplificador operacional al punto de salida del convertidor, entonces el voltaje de salida se puede determinar como

![]() (3.22),

(3.22),

donde k – introducir código digital, norte - profundidad de bits del DAC.

Todos los DAC existentes se dividen en dos grandes grupos: DAC con salida de corriente y DAC con salida de tensión. La diferencia entre ellos radica en la ausencia o presencia de la etapa final en el amplificador operacional en el chip DAC. Los DAC de salida de voltaje son dispositivos más completos y requieren menos componentes adicionales para funcionar. Sin embargo, la etapa final, junto con los parámetros del circuito de escalera, determina los parámetros dinámicos y de precisión del DAC. A menudo es difícil implementar un amplificador operacional preciso de alta velocidad en el mismo chip con un DAC. Por lo tanto, la mayoría de los DAC de alta velocidad tienen una salida de corriente.

No linealidad diferencial para DAC se define como la desviación de la distancia entre dos niveles adyacentes de la señal de salida analógica del valor ideal ULSB . Un gran valor de no linealidad diferencial puede hacer que el DAC se vuelva no monótono. Esto significa que un aumento en el código digital conducirá a una disminución en la señal de salida en alguna parte de la característica (Fig. 3.16). Esto puede conducir a una generación no deseada en el sistema.

|

No linealidad integral para un DAC, se define como la mayor desviación del nivel de la señal de salida analógica de una línea recta trazada a través de los puntos correspondientes al primer y último código, después de que se ajustan.

Tiempo de estabilización DAC se define como el tiempo durante el cual la señal de salida del DAC se establecerá en un nivel determinado con un error de no más de 0,5 ULSB después de que el código de entrada haya cambiado del valor 00…0 al valor 11…1. Si el DAC tiene registros de entrada, una cierta parte del tiempo de establecimiento se debe a un retraso fijo en el paso de las señales digitales, y solo la parte restante se debe a la inercia del propio circuito DAC. Por lo tanto, el tiempo de establecimiento generalmente no se mide desde el momento en que llega un nuevo código a la entrada del DAC, sino desde el momento en que la señal de salida correspondiente al nuevo código comienza a cambiar, hasta el momento en que la señal de salida se establece con una precisión de 0.5U LSB (fig. 3.17) .

|

En este caso, el tiempo de estabilización determina la frecuencia máxima de muestreo del DAC.

(3.23),

donde t S - tiempo de estabilización.

Los circuitos de entrada DAC digital tienen una velocidad finita. Además, la velocidad de propagación de las señales correspondientes a diferentes bits del código de entrada no es la misma debido a la dispersión de los parámetros de los elementos y características del circuito. Como resultado, los brazos del circuito de escalera del DAC, cuando llega un nuevo código, no cambian sincrónicamente, sino con cierto retraso entre sí. Esto lleva al hecho de que en el diagrama de voltaje de salida DAC, al pasar de un valor constante a otro, se observan picos de varias amplitudes y direcciones (Fig. 3.18).

|

|

De acuerdo con el algoritmo de operación, el DAC es un extrapolador de orden cero, cuya respuesta de frecuencia se puede representar mediante la expresión

(3.24),

(3.24),

donde w s - frecuencia de muestreo. La respuesta de frecuencia del DAC se muestra en la Figura 3.20.

|

Como puede verse, a una frecuencia de 0,5w s la señal recuperada se atenúa en 3,92 dB en comparación con los componentes de baja frecuencia de la señal. Por lo tanto, hay una ligera distorsión del espectro de la señal restaurada. En la mayoría de los casos, esta pequeña distorsión no afecta significativamente los parámetros del sistema. Sin embargo, en los casos en que se requiera una mayor linealidad de las características espectrales del sistema (por ejemplo, en sistemas de procesamiento de sonido), para igualar el espectro resultante a la salida del DAC, es necesario instalar un filtro de recuperación especial con una frecuencia respuesta del tipo x/sen(x).